vivado中verilog里关于$readmemb和 $readmemh的使用方法

这两天学习verilog语言时,对 $readmemb和 $readmemh怎么读文件里的数据产生了疑问,网上大多数资料都是inter下quartus里的描述【参考文档1】,也看到一篇vivado开发环境下的文档【参考文档2】,这里也就结合自己的学习汇总一下。

- vivado中verilog里关于$readmemb和 $readmemh的使用方法

- 格式与规则

- 参考文档

格式与规则

在Verilog语法中,$readmemb和 $readmemh一共有以下六种用法:

(1)$readmemb(“<数据文件名>”,<存储器名>);

(2)$readmemb(“<数据文件名>”,<存储器名>,<起始地址>);

(3)$readmemb(“<数据文件名>”,<存储器名>,<起始地址>,<终止地址>);

(4)$readmemh(“<数据文件名>”,<存储器名>);

(5)$readmemh(“<数据文件名>”,<存储器名>,<起始地址>);

(6)$readmemh(“<数据文件名>”,<存储器名>,<起始地址>,<终止地址>);

这里说一下常见的第一种用法和第四种用法:

在vivado里面总共有两种方式实现对指定文件数据的阅读:

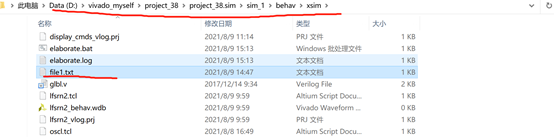

1、相对路径访问:就是把要目标文件放在vivado指定文件键里面,优点不需要特定说明文件位置,缺点就是文件只能放在指定位置下。具体的是在你所建工程的.sim文件夹,然后依次进入sim_1,behav,xsim

D:\vivado_myself\project_38\project_38.sim\sim_1\behav\xsim

D:\vivado_myself\project_38\project_38.sim\sim_1\behav\xsim

文本内容如下:

程序如下:

module test;

reg[3:0] memory_b[0:7];//申请八个四位的存储单元

reg[4:0] i;

initial

begin

$readmemb("file1.txt",memory_b);

for(i=0;i<8;i=i+1)

begin

$display("%memory_b[%0d]=%b",i,memory_b[i]);

end

end

endmodule

然后行为仿真,控制台输出如下:

2、绝对路径访问

可以把目标文件放在系统任意位置,但在 $readmemb和 $readmenh的调用语句里必须指明文件路径。

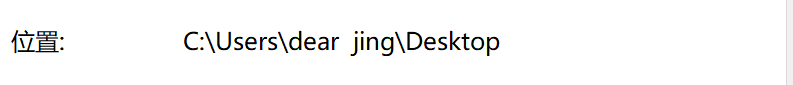

还是上面的file1文件,将其放在桌面。路径为: 程序修改如下:

程序修改如下:

module test;

reg[3:0] memory_b[0:7];//申请八个四位的存储单元

reg[4:0] i;

initial

begin

$readmemb("C:/Users/dear jing/Desktop/file1.txt",memory_b);

for(i=0;i<8;i=i+1)

begin

$display("%memory_b[%0d]=%b",i,memory_b[i]);

end

end

endmodule

输出结果如下:

然后$readmemh就是读十六进制数据,你比如还是读四位一组数据的话,哪里目标文件数据格式应该是像15a0这样的,在语言使用上和前面介绍的一样。

参考文档

链接: link1

链接: link2

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)