用verilog实现minst 的数字识别, 可以用modelsim看结果, 如果要部署到fpga上, PL的资源要非常非常多

代码下载:(包含5个仿真文件)

https://download.csdn.net/download/howard789/13715547

https://github.com/howard789/verilog_mnist

以数字2的仿真文件为例, 可以显示以下的结果,因为最终0-9里 数字2的得分最高,所以判断是2, 这里只是要判断最有可能的数字, 就不再化成几率的形式了

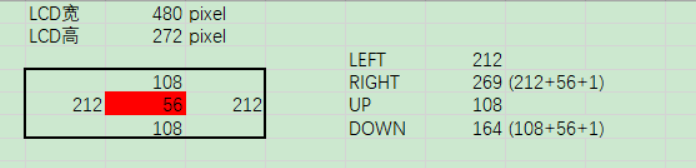

代码里的x坐标和y坐标,是假设在480*272的lcd上显示, 因为minst的像素是28*28的.我们假每4个LCD的像素点代表minst的一个点,那就是在中间红色的区域才是数字显示的区域

部分代码如下,完整代码可以下载

module digital_recognition #(

parameter [10:0] UP = 108,

parameter [10:0] DOWN = 164,

parameter [10:0] LEFT = 212,

parameter [10:0] RIGHT = 269,

parameter [10:0] EACH_WIDE = 2,

parameter DEBIT = 22

)(

//system signals

input clk,

input rst_n,

//binarization

input [ 7:0] dq_i,

input [10:0] xpos,

input [10:0] ypos,

output reg [ 4:0] digit

);

wire res_done_x784;

reg [ 2:0] done_all_res;

reg signed [DEBIT:0] res_0_sum;

reg signed [DEBIT:0] res_1_sum;

reg signed [DEBIT:0] res_2_sum;

reg signed [DEBIT:0] res_3_sum;

reg signed [DEBIT:0] res_4_sum;

reg signed [DEBIT:0] res_5_sum;

reg signed [DEBIT:0] res_6_sum;

reg signed [DEBIT:0] res_7_sum;

reg signed [DEBIT:0] res_8_sum;

reg signed [DEBIT:0] res_9_sum;

//**************************** B输入 *******************************

localparam signed [DEBIT:0] B_0 = - 23'd4599;

localparam signed [DEBIT:0] B_1 = - 23'd3332;

localparam signed [DEBIT:0] B_2 = - 23'd4722;

localparam signed [DEBIT:0] B_3 = - 23'd5087;

localparam signed [DEBIT:0] B_4 = - 23'd3820;

localparam signed [DEBIT:0] B_5 = - 23'd3477;

localparam signed [DEBIT:0] B_6 = - 23'd4286;

localparam signed [DEBIT:0] B_7 = - 23'd3446;

localparam signed [DEBIT:0] B_8 = - 23'd7252;

localparam signed [DEBIT:0] B_9 = - 23'd5047;

assign rst_valid =((xpos == LEFT - 1) && (ypos == UP +1)) || !rst_n;

always @ (posedge clk or negedge rst_n) begin

if(rst_n == 1'b0) done_all_res <= 1'b0;

else done_all_res <= {done_all_res[1:0], res_done_x784};

end

wire add_b;

wire decide_number;

always @ (posedge clk) begin

if(!rst_n)

digit <= 1'b0;

if(done_all_res[2]) begin

/*

$monitor ($time, ,"res_0_sum = %d",res_0_sum);

$monitor ($time, ,"res_1_sum = %d",res_1_sum);

$monitor ($time, ,"res_2_sum = %d",res_2_sum);

$monitor ($time, ,"res_3_sum = %d",res_3_sum);

$monitor ($time, ,"res_4_sum = %d",res_4_sum);

$monitor ($time, ,"res_5_sum = %d",res_5_sum);

$monitor ($time, ,"res_6_sum = %d",res_6_sum);

$monitor ($time, ,"res_7_sum = %d",res_7_sum);

$monitor ($time, ,"res_8_sum = %d",res_8_sum);

$monitor ($time, ,"res_9_sum = %d",res_9_sum);

*/

if ((res_0_sum > res_1_sum ) &&(res_0_sum > res_2_sum ) && (res_0_sum > res_3_sum ) && (res_0_sum > res_4_sum ) && (res_0_sum > res_5_sum ) && (res_0_sum > res_6_sum ) && (res_0_sum > res_7_sum ) && (res_0_sum > res_8_sum ) && (res_0_sum > res_9_sum ) )

digit <= 4'd0;

else if ((res_1_sum > res_0_sum ) &&(res_1_sum > res_2_sum ) &&(res_1_sum > res_3_sum ) &&(res_1_sum > res_4_sum ) &&(res_1_sum > res_5_sum ) &&(res_1_sum > res_6_sum ) &&(res_1_sum > res_7_sum ) &&(res_1_sum > res_8_sum ) &&(res_1_sum > res_9_sum ) )

digit <= 4'd1;

else if ((res_2_sum > res_0_sum ) &&(res_2_sum > res_1_sum ) &&(res_2_sum > res_3_sum ) &&(res_2_sum > res_4_sum ) &&(res_2_sum > res_5_sum ) &&(res_2_sum > res_6_sum ) &&(res_2_sum > res_7_sum ) &&(res_2_sum > res_8_sum ) &&(res_2_sum > res_9_sum ) )

digit <= 4'd2;

else if ((res_3_sum > res_0_sum ) &&(res_3_sum > res_1_sum ) &&(res_3_sum > res_2_sum ) &&(res_3_sum > res_4_sum ) &&(res_3_sum > res_5_sum ) &&(res_3_sum > res_6_sum ) &&(res_3_sum > res_7_sum ) &&(res_3_sum > res_8_sum ) &&(res_3_sum > res_9_sum ) )

digit <= 4'd3;

else if ((res_4_sum > res_0_sum ) &&(res_4_sum > res_1_sum ) &&(res_4_sum > res_2_sum ) &&(res_4_sum > res_3_sum ) &&(res_4_sum > res_5_sum ) &&(res_4_sum > res_6_sum ) &&(res_4_sum > res_7_sum ) &&(res_4_sum > res_8_sum ) &&(res_4_sum > res_9_sum ) )

digit <= 4'd4;

else if ((res_5_sum > res_0_sum ) &&(res_5_sum > res_1_sum ) &&(res_5_sum > res_2_sum ) &&(res_5_sum > res_3_sum ) &&(res_5_sum > res_4_sum ) &&(res_5_sum > res_6_sum ) &&(res_5_sum > res_7_sum ) &&(res_5_sum > res_8_sum ) &&(res_5_sum > res_9_sum ) )

digit <= 4'd5;

else if ((res_6_sum > res_0_sum ) &&(res_6_sum > res_1_sum ) &&(res_6_sum > res_2_sum ) &&(res_6_sum > res_3_sum ) &&(res_6_sum > res_4_sum ) &&(res_6_sum > res_5_sum ) &&(res_6_sum > res_7_sum ) &&(res_6_sum > res_8_sum ) &&(res_6_sum > res_9_sum ) )

digit <= 4'd6;

else if ((res_7_sum > res_0_sum ) &&(res_7_sum > res_1_sum ) &&(res_7_sum > res_2_sum ) &&(res_7_sum > res_3_sum ) &&(res_7_sum > res_4_sum ) &&(res_7_sum > res_5_sum ) &&(res_7_sum > res_6_sum ) &&(res_7_sum > res_8_sum ) &&(res_7_sum > res_9_sum ) )

digit <= 4'd7;

else if ((res_8_sum > res_0_sum ) &&(res_8_sum > res_1_sum ) &&(res_8_sum > res_2_sum ) &&(res_8_sum > res_3_sum ) &&(res_8_sum > res_4_sum ) &&(res_8_sum > res_5_sum ) &&(res_8_sum > res_6_sum ) &&(res_8_sum > res_7_sum ) &&(res_8_sum > res_9_sum ) )

digit <= 4'd8;

else if ((res_9_sum > res_0_sum ) &&(res_9_sum > res_1_sum ) &&(res_9_sum > res_2_sum ) &&(res_9_sum > res_3_sum ) &&(res_9_sum > res_4_sum ) &&(res_9_sum > res_5_sum ) &&(res_9_sum > res_6_sum ) &&(res_9_sum > res_7_sum ) &&(res_9_sum > res_8_sum ) )

digit <= 4'd9;

else

digit <= 4'd10;

end

end

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)