文章目录

- 前言

- 一、Basics:simple wire

-

- 二、Basics:four wires

-

- 三、Basics:Not gate

-

- 四、Basics:And gate

-

- 五、Basics:Nor gate

-

- 六、Basics:Xnor gate

-

- 七、Basics:Wire decl

-

- 八、Baics:7485 chip

-

- 总结

前言

在我学习FPGA之前,看过好多up主讲解怎样学习FPGA,在他们的视频中,总是能不约而同地能看到一个网站的名字:HDL Bits,这是一个训练Verilog语法的网站,可以对语法基础起到很正向的作用,因此我在今天开始,每天都会将HDL Bits中的练习题整理出来,并附上一些自己的理解,如有表述错误,请敬请见谅,并且在评论区告诉我~

注;图片均来自于HDL Bits

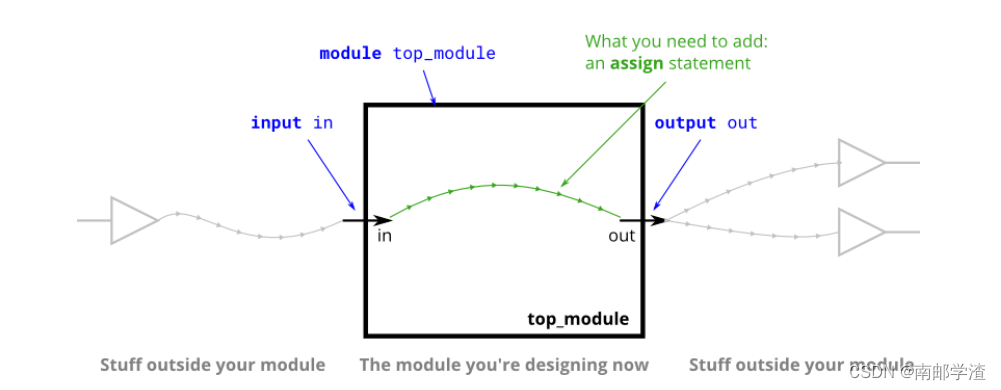

一、Basics:simple wire

线型,与物理导线不同,Verilog中的线型信号是定向的,这意味着信息只向一个方向流动,在连续赋值语句(assign left_side=right_side)中,右边信号的值被驱动到左边的连线上,赋值是连续的,因为即使右边的值发生变化,赋值也会一直持续下去,连续的赋值不是一次性事件,而是连续、一直进行着的。

1.RTL代码

module top_module(

input in,

output out);

assign out = in;

endmodule

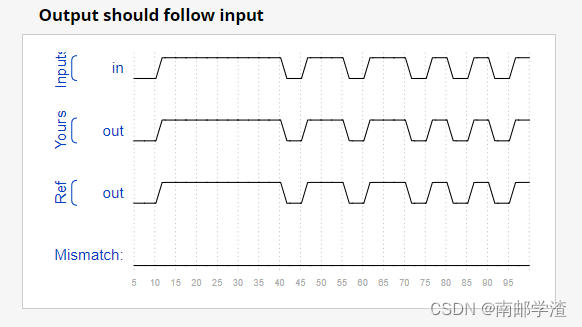

2.仿真波形图

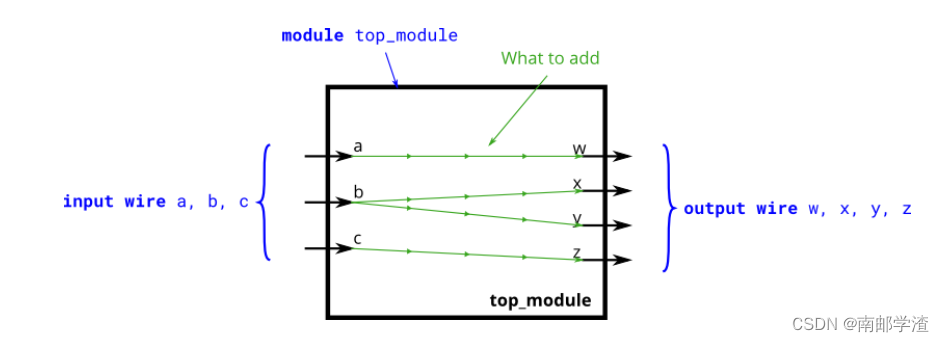

二、Basics:four wires

当你有多个赋值语句时,它们在代码中出现的顺序并不重要,与编程语言不同,赋值语句描述的是事物之间的链接,而不是从一个事物复制到另一个事物的操作。

1.RTL代码

module top_module(

input a,b,c,

output w,x,y,z );

assign w=a;

assign x=b;

assign y=b;

assign z=c;

endmodule

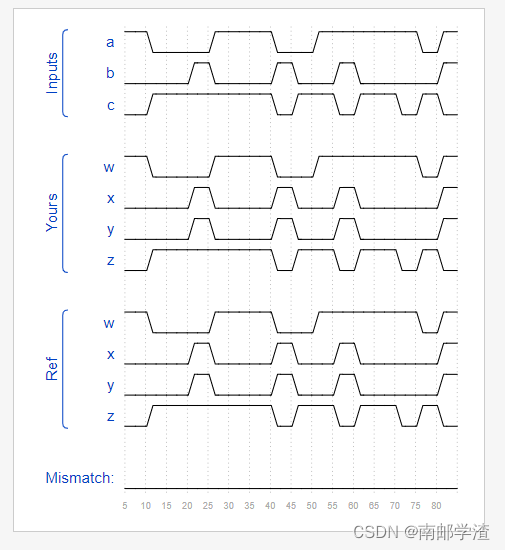

2.仿真波形图

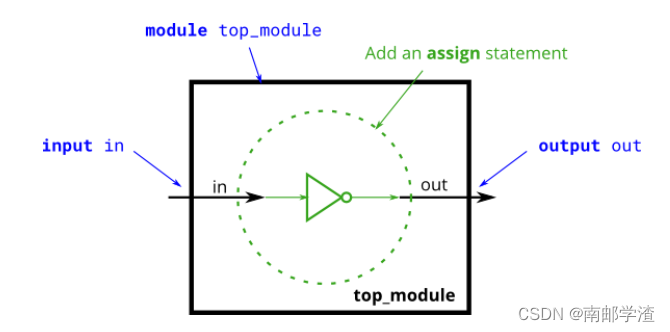

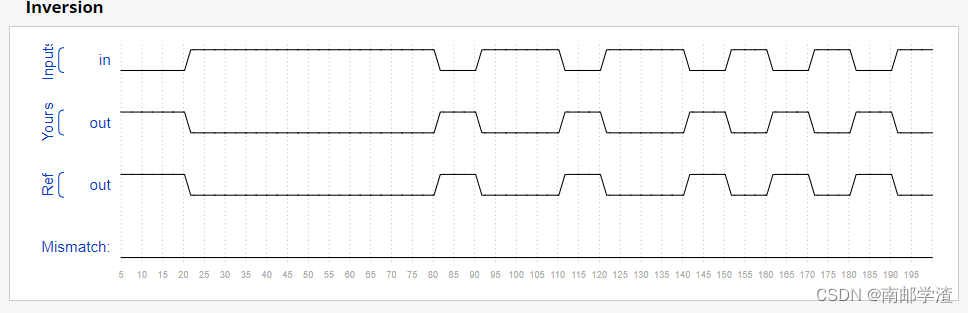

三、Basics:Not gate

Not gate:基本门电路非门,输出等于输入的非

1.RTL代码

module top_module(

input in,

output out );

assign out=~in;

endmodule

2.仿真波形图

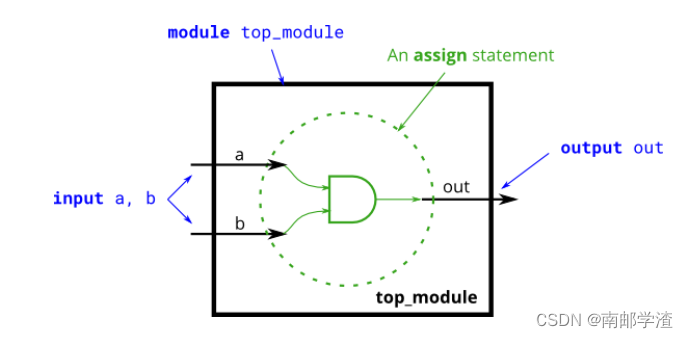

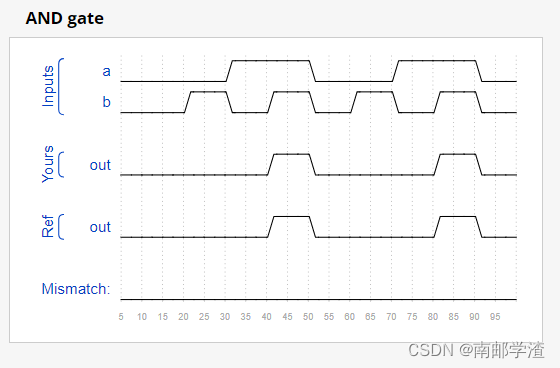

四、Basics:And gate

And gate:基本门电路与门,输出值等于两个输入值的与,a和b全为1时输出为1,否则为0

1.RTL代码

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmodule

或者还可以写成

assign out = (a && b)? 1'b1:1'b0;

2.仿真波形图

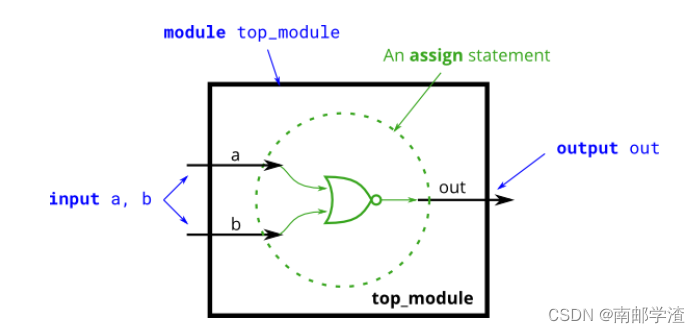

五、Basics:Nor gate

Nor gate:基本门电路或非门:输出等于两个输入的或非,当a和b同时为0时,输出为1,否则都为0

1.RTL代码

module top_module(

input a,

input b,

output out );

assign out = ~(a | b);

endmodule

或者还可以写成

assign out = (a || b)? 1'b0:1'b1;

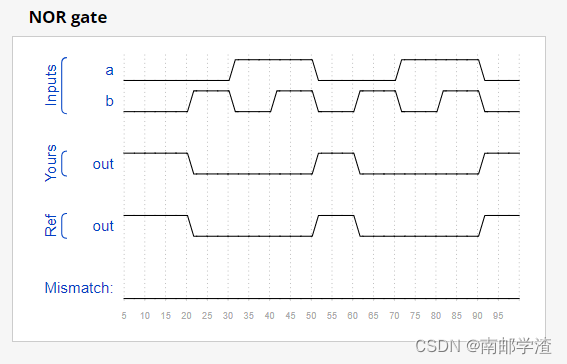

2.仿真波形图

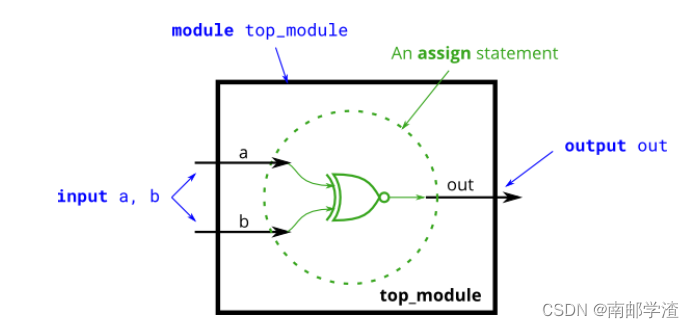

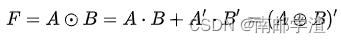

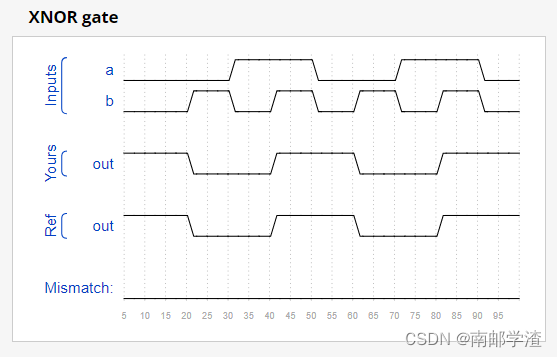

六、Basics:Xnor gate

Nor gate:基本门电路同或门

1.RTL代码

module top_module(

input a,

input b,

output out );

assign out = (a & b) | (~a & ~b);

endmodule

2.仿真波形图

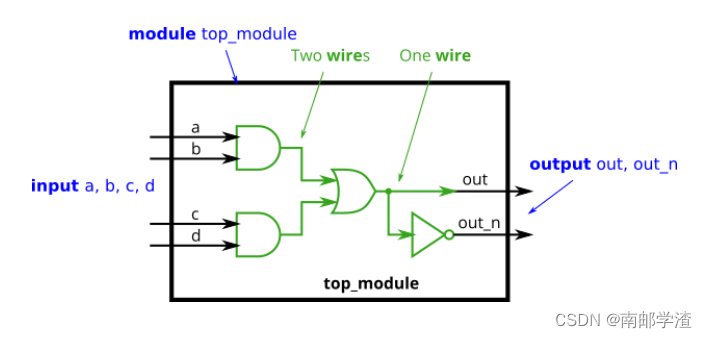

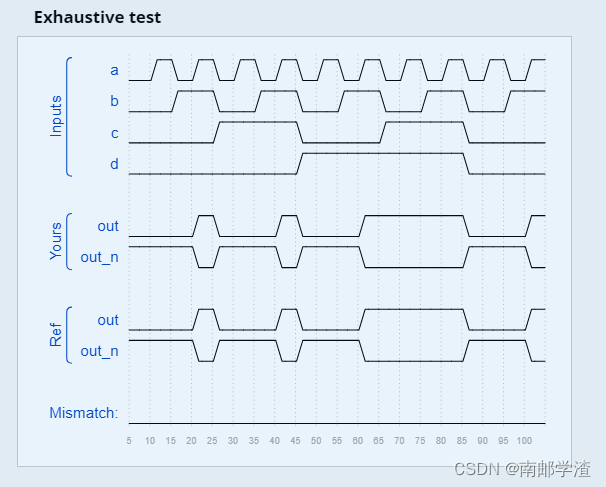

七、Basics:Wire decl

本次训练是声明wire型信号,随着电路变得越来越复杂,将需要电线来连接内部元件。 当需要使用连线时,应该在模块体中声明它,在它第一次被使用之前的某个地方。

1.RLT代码

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire w1;

wire w2;

wire w3;

assign w1 = a & b;

assign w2 = c & d;

assign w3 = w1 | w2;

assign out = w3;

assign out_n = ~w3;

endmodule

2.仿真波形图

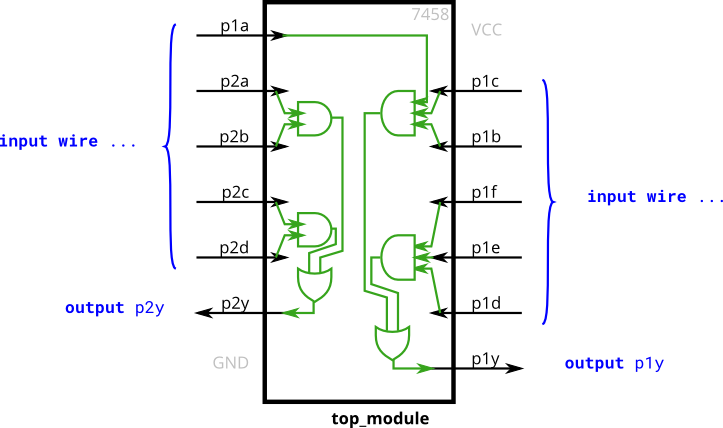

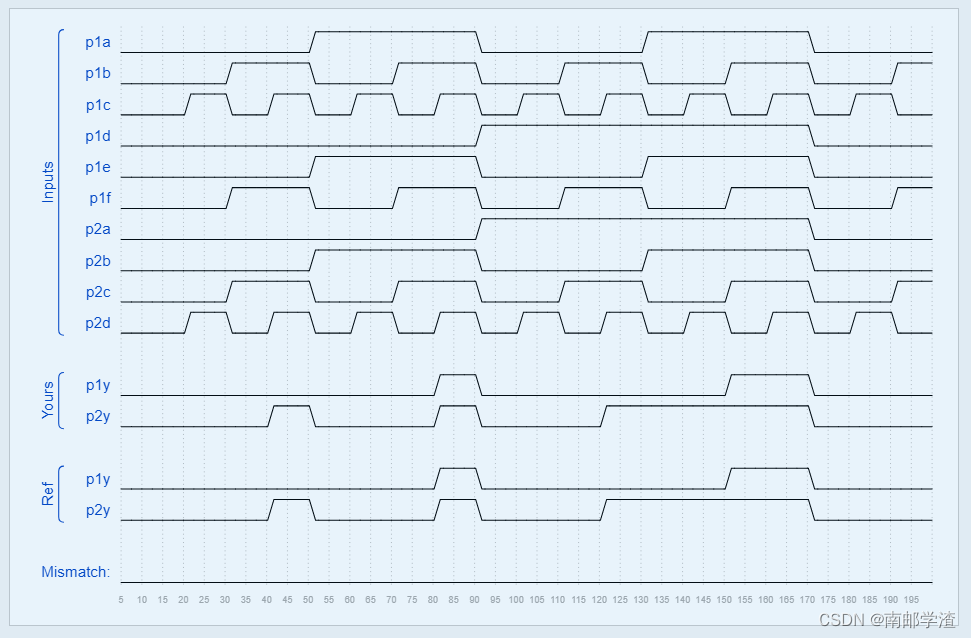

八、Baics:7485 chip

7485 chip:7485比较器芯片,可根据门电路组合直接写出代码

1.RTL代码

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = (p1a & p1b & p1c) | (p1d & p1e & p1f);

assign p2y = (p2a & p2b) | (p2c & p2d);

endmodule

2.仿真波形图

总结

本章节的八个小设计是很简单也很基础的设计,代码写法可以多种多样,但要养成良好的代码编写习惯,才可以走得更远。

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)