基于Xilinx XDMA 的PCIE通信

概述:

想实现基于FPGA的PCIe通信,查阅互联网各种转载…基本都是对PCIe的描述,所以想写一下基于XDMA的PCIe通信的实现(PCIe结构仅做简单的描述(笔记),了解详细结构移至互联网)。实践实践!!!

说明:

参考文档:

PCI Express Base Specification Revision 3.0

PCI Express Base Specification Revision 5.0

pg195-pcie-dma

PCI Express体系结构导读

环境:Vivado2019.2。

第一篇:基于Xilinx XDMA 的PCIE通信

第二篇:基于XDMA 的PCIE读写DDR

直通☛ 200页+ FPGA/IC秋招面试笔试题

一、读写BRAM实例

读写文件:

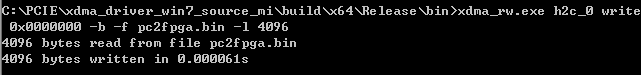

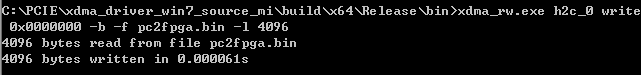

1、PC通过CMD执行以下命令,将 pc2fpga.bin 文件下的4096Byte写入FPGA 起始地址为0x00000000:

xdma_rw.exe h2c_0 write 0x0000000 -b -f pc2fpga.bin -l 4096

pc2fpga.bin文件内容如下所示:

PC通过CMD执行以下命令(TX):

FPGA数据接收(RX):

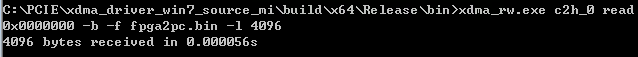

2、PC通过CMD执行以下命令,从FPGA读取4096Byte写入到PC的 fpga2pc.bin 文件里:

xdma_rw.exe c2h_0 read 0x0000000 -b -f fpga2pc.bin -l 4096

PC通过CMD执行以下命令(RX):

观察在cmd访问的文件夹下,接收并创建了fpga2pc.bin文件,大小为4KB

接收到的数据fpga2pc.bin 如下所示:

FPGA端正在上传的数据(TX):

FPGA上传的数据是怎么产生的?

PC端接收到的数据是FPGA提前写入BRAM的数据,当PC下发读取指令时即读取的为BRAM的数据,那我们BRAM提前写入的是什么呢?提前通过RTL代码将一下数据写入BRAM0。

则BRAM中的数据为:

| 0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

a |

b |

c |

d |

e |

f |

| 00h |

00 |

00 |

00 |

00 |

04 |

04 |

04 |

04 |

08 |

08 |

08 |

08 |

0c |

0c |

0c |

| 10h |

10 |

10 |

10 |

10 |

14 |

14 |

14 |

14 |

18 |

18 |

18 |

18 |

1c |

1c |

1c |

| 20h |

20 |

20 |

20 |

20 |

24 |

24 |

24 |

24 |

28 |

28 |

28 |

28 |

2c |

2c |

2c |

再对比读回来的数据,无误。

读写数据:

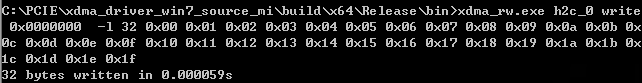

3、PC通过CMD执行以下命令,写32Byte

0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0a 0x0b 0x0c 0x0d 0x0e 0x0f 0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x19 0x1a 0x1b 0x1c 0x1d 0x1e 0x1f

的数据到FPGA:

xdma_rw.exe h2c_0 write 0x0000008 -l 32 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0a 0x0b 0x0c 0x0d 0x0e 0x0f 0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x19 0x1a 0x1b 0x1c 0x1d 0x1e 0x1f

PC端 cmd输入(TX):

FPGA数据接收(RX):

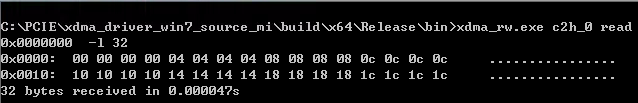

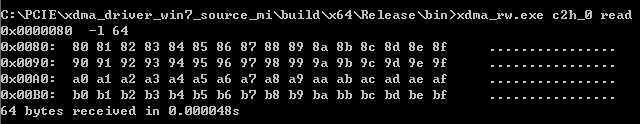

4、PC通过CMD执行以下命令,读取32Byte的数据到PC:

xdma_rw.exe c2h_0 read 0x0000000 -l 32

PC端 cmd输入(RX):

FPGA正在上传的数据(TX):

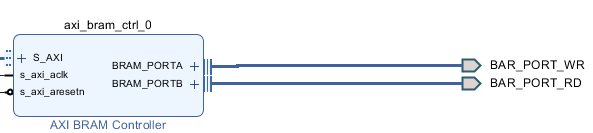

2.5.2 BAR空间的访问

对应的是对BAR_PORT的操作。

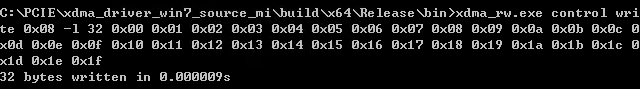

1、PC通过CMD执行以下命令,通过PCIe BAR空间将4Byte数据映射到AXI_Lite寄存器:

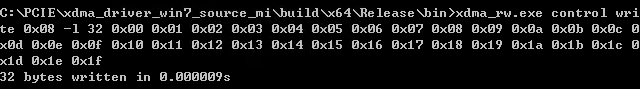

xdma_rw.exe control write 0x08 -l 32 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0a 0x0b 0x0c 0x0d 0x0e 0x0f 0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x19 0x1a 0x1b 0x1c 0x1d 0x1e 0x1f

PC端 cmd输入(TX):

FPGA接收的数据(RX):

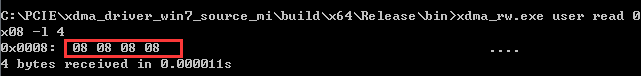

2、PC通过CMD执行以下命令,PCIe BAR空间访问AXI_Lite寄存器读取4Byte的数据:

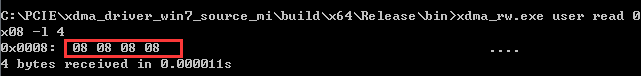

xdma_rw.exe user read 0x08 -l 4

PC端 cmd输入(RX):

观察接收到FPGA返回的数据为0x08080808.

观察FPGA正在上传的数据(TX):

无误。

二、读写DDR实例

1、PC通过CMD执行以下命令,将 pc2fpga.bin 文件下的4096Byte写入DDR起始地址为0x00000000:

xdma_rw.exe h2c_0 write 0x0000000 -b -f pc2fpga.bin -l 4096

pc2fpga.bin文件内容如下所示:

PC通过CMD执行以下命令(TX):

验证数据是否写入DDR,我们通过逻辑代码进行DDR数据的读取:

从地址0000_0000h读取大小为4096Byte的数据。

观察源文件其实就是斜坡数据。

观察第一个256bit数据为:

最后一个256bit数据为:

在PC CMD端输入以下指令也读取DDR数据,与用户读取的数据进行对比,无误。

xdma_rw.exe c2h_0 read 0x0000000 -l 4096

CMD读取的数据:

2、通过VIO输入地址和数据大小,进行相应的DDR数据读取。

从地址0000_0080读取64Byte的数据,即512bit数据。

。

对比PC端读取DDR0000_0080读取64Byte的数据,一样的✌

3、FPGA端通过VIO实现从DDR任意地址,任意地址大小数据的读取。

user_raddr:通过VIO写入要读取DDR数据的地址。

user_rsize:通过VIO写入要读取DDR数据的大小(单位为Byte)。

user_rexe:点击一次,执行一次读操作。

5.2 BAR空间的访问

1、PC通过CMD执行以下命令,通过PCIe BAR空间将4Byte数据映射到AXI_Lite寄存器:

xdma_rw.exe control write 0x08 -l 32 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0a 0x0b 0x0c 0x0d 0x0e 0x0f 0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x19 0x1a 0x1b 0x1c 0x1d 0x1e 0x1f

PC端 cmd输入(TX):

FPGA接收的数据(RX):

2、PC通过CMD执行以下命令,PCIe BAR空间访问AXI_Lite寄存器读取4Byte的数据:

xdma_rw.exe user read 0x08 -l 4

PC端 cmd输入(RX):

观察接收到FPGA返回的数据为0x08080808.

观察FPGA正在上传的数据(TX):

无误。