同步、异步复位的概念是重要的基础内容,需对其有较清晰的认识,才能在复位电路的设计时得心应手,本文基于前辈分享,结合自己的理解,浅谈亚稳态、复位电路等相关内容。

首先需要明确的是,同步、异步名词背后的两个对象是谁,谁和谁同,谁和谁异。复位的目标是将寄存器、RAM等单元恢复初始状态,重点应该在于这些单元的输出变成初始状态,所以同步、异步实际上说的是输出信号和时钟之间的关系。

不要理解为:复位信号和时钟之间的关系。

同步复位

代码层面理解:always块的敏感列表中只有时钟信号sys_clk,所以想要触发复位的前提是sys_clk信号高电平有效,基于此前提,复位后的输出信号一定是和sys_clk信号同步的。

RTL代码:

module Sync_rst (

input sys_clk,

input sys_rst, // Synchronous reset

input [7:0] d,

output reg [7:0] q

);

always@(posedge sys_clk) begin

if (!sys_rst) q <= 8'b0;

else q <= d;

end

endmodule

tb文件:

module tb_sync_rst();

reg sys_clk ;

reg sys_rst ;

reg [7:0] d ;

wire [7:0] q ;

Sync_rst Sync_rst_init(

.sys_clk (sys_clk),

.sys_rst (sys_rst), // Synchronous reset

.d (d),

.q (q)

);

always #10 sys_clk = ~sys_clk;

initial begin

sys_clk = 1'b0;

sys_rst = 1'b1;

d = 'd1;

#45

sys_rst = 1'b0;

#50

sys_rst = 1'b1;

end

endmodule

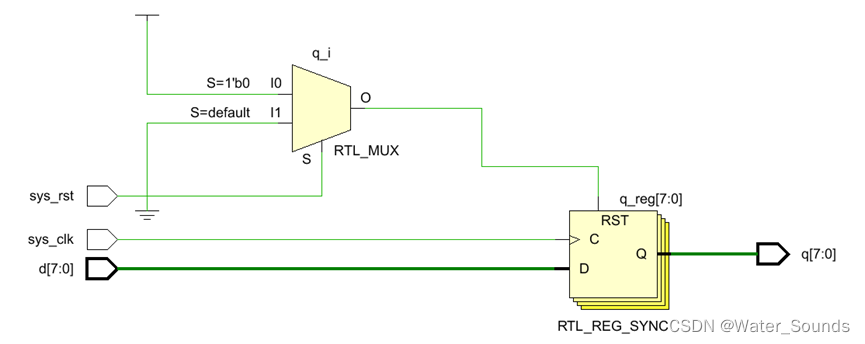

综合后电路理解

使用Vivado综合电路如下所示,它看起来很像异步复位,这是因为图中展示的RTL_REG_SYNC是带有同步复位引脚的触发器,标志是RST口。

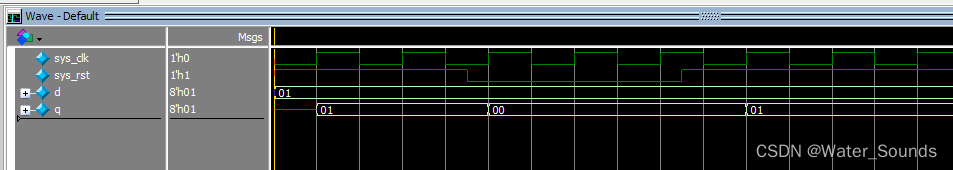

图中,q从1变到0的边沿和sys_clk是对齐的,即为“同步”。

同步复位的优点:

- 复位信号的毛刺不会影响时序,抗干扰能力强。

- 有利于仿真器仿真

- 有利于时序分析

同步复位缺点:

- 只有在时钟沿到来时复位信号才起作用,复位信号持续的时间应该超过一个时钟周期才能确保系统复位,同时还要考虑组合逻辑路径延时,复位延时等因素。

- 如果逻辑器件没有同步复位端口,则会因为插入组合逻辑耗费较多的逻辑资源。

异步复位

代码层面理解:always块的敏感列表中既有时钟信号sys_clk还有sys_rst信号。

RTL代码:

module Async_rst (

input clk,

input rst_n, // asynchronous reset

input [7:0] d,

output reg [7:0] q

);

always@(posedge clk or negedge rst_n) begin

if (!rst_n) q <= 8'b0;

else q <= d;

end

endmodule

tb文件:

`timescale 1ns / 1ps

module tb_sync_rst();

reg sys_clk ;

reg sys_rst ;

reg [7:0] d ;

wire [7:0] q ;

Async_rst Async_rst_init(

.clk (sys_clk),

.rst_n (sys_rst), // Synchronous reset

.d (d),

.q (q)

);

always #10 sys_clk = ~sys_clk;

initial begin

sys_clk = 1'b0;

sys_rst = 1'b1;

d = 'd1;

#45

sys_rst = 1'b0;

#50

sys_rst = 1'b1;

end

endmodule

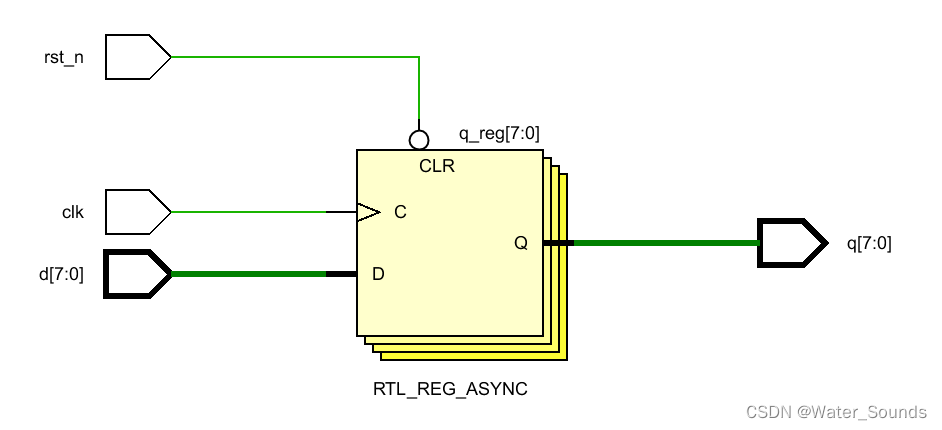

综合电路理解:

典型的异步复位电路,区别于上面同步复位的电路图,它是CLR口。

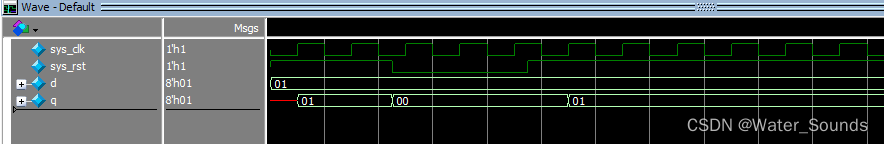

上图中q从1变为0的边沿和时钟信号的边沿是异步的。

异步复位的优点:

- 无需额外的逻辑资源,实现简单。

- 复位信号不依赖于时钟。

异步复位缺点:

3. 复位信号容易受到外界的干扰,如毛刺等影响。

4. 复位信号释放的随机性,可能导致时序违规,倘若复位释放时恰恰在时钟有效沿附近,就很容易使电路处于亚稳态。

建立时间、保持时间、恢复时间、去除时间

同步系统中会涉及到前两个时间,因为无论是控制信号还是数据信号,都需要提前保持稳定,等待CLK触发,再继续保持稳定,触发器的输出才是稳定的。

建立时间:setup time,是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间。在时钟信号上升沿到来之前,数据需要提前稳定住自己,为写入触发器做准备,这段提前准备的时间就是建立时间。

保持时间:hold time,是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间。在时钟信号上升沿到来之后,数据需要继续稳定住自己,保证能够写入触发器,这段继续稳定的时间就是保持时间。

无论是数据还是控制信号,在输入触发器时,只有同时满足建立时间和保持时间,才能保证触发器的输出是稳定的。

异步系统中会涉及到后两个时间,因为某一个时钟上升沿到底能否有效驱动工作,取决于时钟信号和复位信号之间是否满足恢复时间或者去除时间。

恢复时间:recovery time,原本有效的复位信号释放后,与紧跟其后的第一个时钟上升沿之间的最小时间。复位信号释放后,至少经过恢复时间这么长时间后,系统才能在下一个时钟信号上升沿开始工作,如果复位信号释放和下一个时钟上升沿离得太近,系统就不能从复位状态中恢复过来。

去除时间:removal time,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近(但在这个时钟沿之后),那么就不能保证有效地屏蔽这个“时钟沿”,也就是说这个“时钟沿”可能会起作用。

换句话来说,如果你想让某个时钟沿起作用,那么你就应该在“恢复时间”之前是异步控制信号变无效,如果你想让某个时钟沿不起作用,那么你就应该在“去除时间”过后使控制信号变无效。如果你的控制信号在这两种情况之间,那么就没法确定时钟沿是否起作用或不起作用了,也就是说可能会造成寄存器处于不确定的状态。而这些情况是应该避免的。所以恢复时间和去除时间是应该遵守的。

CSDN链接: 恢复和去除时间(Recovery and Removal Time)

亚稳态

产生的原因:在FPGA系统中,如果数据传输中不满足触发器的Tsu(建立时间)和Th(保持时间)不满足,或者复位过程中的去除时间、复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值

发生场合:只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

链接: FPGA中亚稳态【Tsu建立时间setup】【Th保持时间hold】【Tmet决断时间】【recovery恢复时间】【removal移除时间】【复位】

链接: 不得不读的 FPGA 设计白皮书——Xilinx FPGA 复位策略白皮书翻译(WP272)【FPGA探索者】

异步复位,同步释放

异步复位、同步释放是指复位信号产生时不受时钟信号的控制,但是释放的时候受到时钟信号的同步。主要目的是防止复位信号释放时候产生亚稳态。

异步复位:当复位信号拉低时,直接进入复位状态。

同步释放:当复位信号释放时,加入两级同步缓存器,电路不会立即释放,而是同步到时钟有效时再进行释放。

链接: 异步复位,同步释放