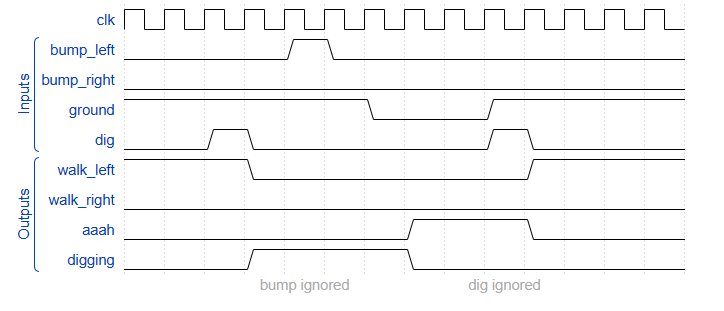

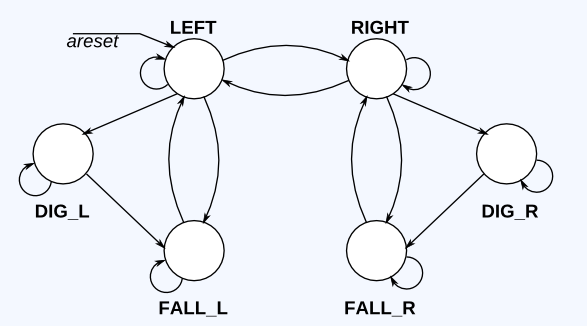

In addition to walking and falling, Lemmings can sometimes be told to do useful things, like dig (it starts digging when dig=1). A Lemming can dig if it is currently walking on ground (ground=1 and not falling), and will continue digging until it reaches the other side (ground=0). At that point, since there is no ground, it will fall (aaah!), then continue walking in its original direction once it hits ground again. As with falling, being bumped while digging has no effect, and being told to dig when falling or when there is no ground is ignored.

(In other words, a walking Lemming can fall, dig, or switch directions. If more than one of these conditions are satisfied, fall has higher precedence than dig, which has higher precedence than switching directions.)

Extend your finite state machine to model this behaviour.

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

input dig,

output walk_left,

output walk_right,

output aaah,

output digging );

parameter LEFT = 3'b000,

DIG_L = 3'b110,

FALL_L = 3'b111,

RIGHT = 3'b001,

DIG_R = 3'b010,

FALL_R = 3'b011;

reg [2:0] state;

reg [2:0] next_state;

always@(*)

case (state)

LEFT:

if(ground == 0)

next_state <= FALL_L;

else if(dig)

next_state <= DIG_L;

else if(bump_left)

next_state <= RIGHT;

else

next_state <= LEFT;

DIG_L:

if(ground == 0)

next_state <= FALL_L;

else

next_state <= DIG_L;

FALL_L:

if(ground == 0)

next_state <= FALL_L;

else if(ground == 1)

next_state <= LEFT;

else

next_state <= FALL_L;

RIGHT:

if(ground == 0)

next_state <= FALL_R;

else if(dig)

next_state <= DIG_R;

else if(bump_right)

next_state <= LEFT;

else

next_state <= RIGHT;

DIG_R:

if(ground == 0)

next_state <= FALL_R;

else

next_state <= DIG_R;

FALL_R:

if(ground == 0)

next_state <= FALL_R;

else if(ground == 1)

next_state <= RIGHT;

else

next_state <= FALL_R;

default:

next_state <= LEFT;

endcase

always@ (posedge clk or posedge areset)

if(areset)

state <= LEFT;

else

state <= next_state;

assign digging = (state == DIG_R || state == DIG_L);

assign aaah = (state == FALL_L || state == FALL_R);

assign walk_left = (state == LEFT );

assign walk_right = (state == RIGHT );

endmodule