标准数字逻辑IC集成电路可以从工艺、功能和电平三个方面划分,列表所示。

注:常见的逻辑电路有54军用系列和74商用系列,两者电路功能一致,本文仅讨论74系列。

按照制造工艺特点分类:

| 工艺 |

逻辑器件产品族 |

优点 |

不足 |

| Bipolar |

TTL、S、LS、AS、F、ALS、ECL |

速度快,强电流驱动能力,工艺简单。 |

功耗较大,集成度相对较低。 |

| CMOS |

HC、HCT、CD4000、ACL、FCT、LVC、LV、CBT、ALVC、AHC、AHCT、CBTLV、AVC、GTLP |

功耗低、抗干扰能力强,集成度高。 |

输入电流过大(≥40mA)容易造成锁定效应,造成芯片烧毁。 |

| BiCMOS |

BCT、ABT、LVT、ALVT |

高速度,低功耗。 |

工艺极其复杂,造价昂贵。 |

表 1 通用逻辑器件工艺特点

Bipolar:

全用三极管实现电路。是纯种双极工艺,双极工艺的主要特点是速度快,电流驱动能力强。

CMOS:

全用MOS管实现电路。指互补金属氧化物(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造工艺,由于CMOS中一对MOS组成的门电路在瞬间看,要么PMOS导通,要么NMOS导通,要么都截至,比线性的三极管效率要高得多,因此功耗很低,集成度高。

BiCMOS:

既有MOS管,也有三极管。是CMOS和双极器件同时集成在同一块芯片上的技术,其基本思想是以CMOS器件为主要单元电路,而在要求驱动大电容负载之处加入双极器件或电路,可以使电路达到高速度、低功耗。

工艺复杂程度:BiCMOS > Bipolar > CMOS

图1 标准逻辑产品应用示意图

从逻辑产品族角度分析,TTL产品功耗比较大,会慢慢淡出市场。AUP产品功耗最低,AUC产品速度最快。如图1所示,LVC和LV产品应用范围最广,是目前市场上的主流产品。CD4000产品电压范围最大,最高可达15V。

1)按照功能分类:

| 功能 |

逻辑器件 |

应用场景 |

备注 |

| 门电路/反相器 |

与门74X08、与非门74X00、或门74X32、或非门74X02、异或门74X86、反相器:74X04 |

逻辑门电路一般用于控制各种模块及系统间通信,如交换机复位系统中。 |

|

| 触发器 |

J-K触发器、带三态的D触发器74X374、不带三态的D触发器74X74、施密特触发器等。 |

交换机中多用于POE按键切换电路。 |

|

| 选择器 |

2-1、4-1、8-1选择器74X157、74X153、74X151等。 |

解决不同I2C设备的地址冲突,不同I2C共享一个负载。隔离不同电压工作的I2C。 |

|

| 编/译码器 |

2/4、3/8和4/16译码器74X139、74X138、74X154等。 |

/ |

|

| 寄存器 |

串-并移位寄存器74X164、并-串寄存器74X165等。 |

交换机中多用于LED电路。 |

|

| 缓冲驱动器 |

带反向的缓冲驱动器74X240、不带反向的缓冲驱动器74X244。 |

不执行任何运算,输出与输入值一致。使高速工作的IC与慢速工作的外设起协调,同步和缓冲的作用。 |

增强驱动能力。 |

| 收发器 |

寄存器收发器74X245、通用收发器74X245、总线收发器等。 |

/ |

|

| 转换器 |

单向电平转换、双向电平转换和逻辑电平转换。 |

能将较高逻辑电平转换成较低逻辑电平,实现不同工作电压IC连接和数据通讯。 |

|

| 总线开关 |

包括总线交换和通用总线器件等。 |

总线开关在高速数据接口中应用较多,用来导通或者阻隔数字信号。 |

|

表 2 通用逻辑器件按照使用功能分类

注:74X164中的X代表逻辑产品族。

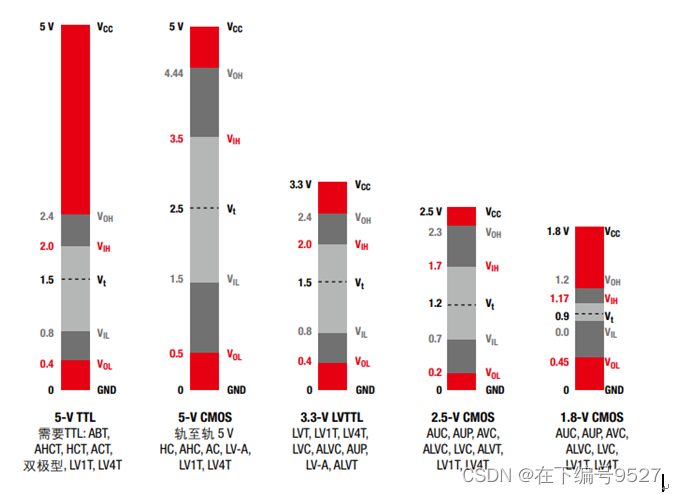

2)按照电平种类分类

| 电平 |

逻辑器件产品族 |

| 0.8V |

AUC、AUP |

| 1.2V |

AUC、AUP、AVC |

| 1.5V |

AUC、AUP、AVC |

| 1.8V |

ALVC、AUC、AUP、AVC、LVC、LV1T |

| 2.5V |

ALVC、ALVT、AUC、AUP、AVC、CBTLV、LV、LV1T、LV-A、LVC |

| 3.3V |

AC、AHC、ALB、ALVC、ALVT、AUP、AVC、CBLTV、LV、LV-A、LVC、LVT、LV1T、AUP1T |

| 5V |

ABT、AC/ACT、AHC、AHCT、ALS、AS、BCT、CBT、F、LV、LV1T、LV-A、LS、S、TTL、CD4K、FCT2 |

| 5V以上 |

CD4000 |

| 特殊逻辑器件 |

BTL、ETL、GTL、GTLP、HSTL、SSTL、SSTV、TVC、VME、LSF |

表3 逻辑器件产品按电平分类

注:逻辑器件产品族名词解释见3.1.5

3)开关标准的比较

逻辑器件开关标准比较:

图2 开关标准比较

4)逻辑器件性能比较

在对驱动能力和速度要求较高的场合,如高速总线型信号线,可使用ABT、LVT系列。在选择驱动器件的驱动能力和速度时,不能盲目追求大驱动能力和高速的器件,应该选择能够满足设计要求,同时有一定的余量的器件,这样可以减少信号过冲,改善信号质量。并且在设计时必须考虑信号匹配,故选型时应根据产品需求考虑选取最合适的逻辑产品族。

| 逻辑产品族 |

工作电压范围 |

驱动电流 |

速度 |

| AHC(低功耗) |

2.0 V至5.5 V |

4mA(在3.3 V电压下) 8mA(在5 V电压下) |

典型值为150MHz (在5V电压下) |

| LVC(高驱动能力) |

1.65 V至5.5V |

24mA(在3.3V电压下) 32mA(在5.0V电压下) |

典型值为250MHz (在5V电压下) |

| AUP(极低的功耗-在3.3V电压条件下小于0.9μA) |

0.8V至3.6V |

1.9mA(在1.5 V电压下) 4mA(在3.3V电压下) |

典型值为190MHz (在3.3V电压下) |

| AUC(极快的速度) |

0.8V至2.7V |

5mA(在1.5 V电压下) 9mA(在2.5V电压下) |

典型值为350 MHz (在2.5V电压下) |

表4 逻辑产品族工作性能对比

5)逻辑器件技术的介绍

标准逻辑门器件的优势有很多:如带有施密特触发器逻辑门输入允许任意的上升及下降时间斜率;斜漏极开路输出可以实现升压或者降压转换;Ioff能支持热插拔,当VCC处于0V时,Ioff可在输入或者输出端上提供电压。下面主要介绍总线保持输入功能和施密特触发器。

总线保持输入

主要特点:

- 保持输入的最后已知状态——避免使输入悬空;

- I(HOLD)或IBHL和IBHH确定了最小保持电流;

- 在有效逻辑电平条件下,保持电流并未给驱动输出施加很重的负载;

- 在未用或悬空输入/输出引脚上,不需要增设外部电阻;

- 器件名称中的“H”表示总线保持;

- 系统功耗的增加微乎其微;

- 总线保持输入单元取代了上拉电阻。

具有总线保持选项的器件系列:

ABT、ALVC、ALVT、AVC、AUC、FCT、GTL、GTLP、LVC、LVT、VME

图3 总线保持示意图

施密特触发器

大多数CMOS、BICMOS和TTL逻辑器件都要求快速的输入边沿,逻辑器件上电或使用按键开关的时候,慢边沿是不可避免的,当输入缓慢变化的信号,逻辑器件会出现误判动作,这是可以通过施密特触发器来防止此现象。

主要特点:

- 可以减低噪声的干扰

- 将缓慢的信号变成陡峭的矩形信号

现有的比较器以一个基准点为基础区分高电平/低电平状态。如果电压在基准点附近晃动,则显示不稳定,输入端有噪声来回多次穿越临界电压时,输出端即受到干扰,其正负状态产生不正常转换。如图4所示,在比较器上加入Feedback电阻,输出电压(Vout)改变了基准电压(Vth)。所谓施密特触发器,就是包含正反馈的比较器电路。

图4 施密特触发器简化模型和阔值电压的设定

施密特触发器采用电位触发方式,其状态由输入信号电位维持;对于负向递减和正向递增两种不同变化方向的输入信号,施密特触发器有不同的阀值电压。如图5所示比较器只有一个临界电压,蓝色圈的杂波噪声穿越了临界电压,当输入电压从低电平上升到阈值电压或从高电平下降到阈值电压时,电路的状态将发生变化。

图5 施密特触发器的使用场景

2.标准逻辑门器件

逻辑门电路相关器件由与门、或门和非门(反相器)以及其组合形态组成,一般用于控制各种模块及系统是网通/数通产品最基础的功能之一,其品质、性能往往与系统的稳定性关联,直接影响产品的品质和性能。针对通用逻辑类器件品类多样、应用各异、品质不一、性能及成本也不尽相同等常见选型困惑及相关疑问,本选型指导旨在为交换机硬件设计在通用逻辑类器件选型评估、测试验收、性能提升、品质加固及成本控制提供全面指导,以实现在最优成本条件下,产品硬件设计选型满足各种复杂的环境考验,提高产品的稳定性、可靠性等综合竞争力。

2.1 器件原理介绍

门电路是用于实现基本逻辑运算和复合逻辑运算的单元电路。早期用二极管和三极管搭建的分立门电路,目前应用比较多的是集成门电路。晶体管是构成现代集成电路的基本元件,分为双极晶体管和单极晶体管。

2.1.1 TTL门电路

TTL电路,指输入输出级都使用晶体管,由两个PN结组成,双极结型晶体管有两种基本结构:PNP型和NPN型。图6所示,中间一层称为b基极,e发射集,c集电极。三极管有很多特性,本文只关注开关特性,使其工作在饱和区和截止区就可以满足我们的需求。

图6 PNP型和NPN型三极管

从图7可以看出,TTL与非门电路基本结构由三部分构成:输入级、中间级和输出级。因为电路的输入端和输出端都是三极管结构,所以称这种结构的电路为三极管---三极管逻辑电路。

图7 双极晶体管组成的反相器典型电路

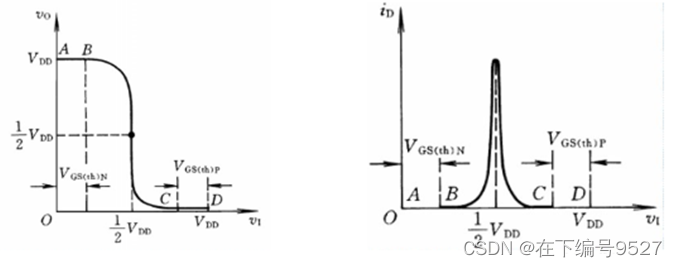

2.1.2 CMOS门电路

场效应管是单极晶体管,通常用金属氧化物半导体场效应晶体管(MOSFET),也就是我们常说的MOS管作为开关器件。MOS管为压控型有三个极性,源极S(Source)和漏极D(Drain),另外一个电极栅极G(Gain)。MOS管的导通则由G和S极之间的压差决定。MOS管分为NMOS和PMOS两种类型。

图8 MOS晶体管的类型

用这两种功能相对应的晶体管就构成了互补型的MOS集成电路,也简称为CMOS集成电路(Complementary MOS)。图9所示,A端为高电平时,P型管截止,N型管导通,输出端Y的电平与GND保持一致,Y端输出低电平; A端为低电平时,P型管导通,N型管截止,输出端Y的电平与VDD保持一致,Y端输出高电平。由NMOS管和PMOS管组成的非门,也叫反相器。反相器的栅端(G)相连作为输入端,漏断相连作为输出端,NMOS的源端接地,PMOS的源端接电源VDD。

图9 非门原理图与真值表

图10 反相器的电压、电流传输特性

3.1 典型通用逻辑器件电气特性介绍

| 电气特性 |

TTL门电路 (以74XX00为例) |

CMOS门电路 (以74XX04为例) |

| 74、74S、74LS、74AS、74ALS、74F系列 |

74HC04、 74AHC04 |

74HCT04、 74AHCT04 |

| 工作电压范围 |

5.25V |

HC:2~6V AHC:2~5.5V |

4.5~5.5V |

| 输入低电平的上限值 VIL(max) |

0.8V |

1.35V |

0.8V |

| 输出低电平的上限值 VOL(max) |

0.4V |

HC:0.33V AHC:0.44V |

HCT:0.33V AHCT:0.44V |

| 输入高电平的下限值 VIH(min) |

2.0V |

3.15V |

2.0V |

| 输出高电平的下限值 VOH(min) |

74系列2.4V 其余2.7V |

4.4V |

4.4V |

| 输出最低电流 IOL (Max) |

-0.4mA |

CMOS负载:-0.02mA TTL负载:-4mA |

CMOS负载:-0.02mA TTL负载:-4mA |

| 输出最高电流 IOH (Max) |

8mA |

CMOS负载:0.02mA TTL负载:4mA |

CMOS负载:0.02mA TTL负载:4mA |

| ICC (Max) |

0.1~2uA |

0.1~2uA |

0.1~2uA |

| 高电平噪声容限 VNH/V VNH=VOH(min)-VIH(min) |

74系列0.4V 其余0.7V |

1.25V |

2.4V |

| 低电平噪声容限 VNL/V VNL=VIL(max)-VOL(max) |

0.4V |

HC:1.02V AHC:0.91V |

HCT:0.47V AHCT:0.36V |

表 5 典型逻辑器件电气特性

注:以实际的器件手册中的参数为准

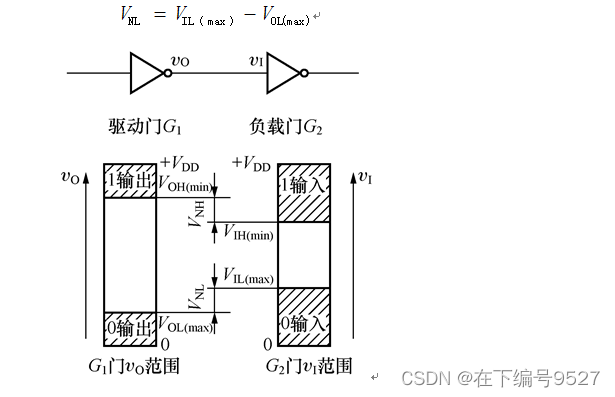

3.2 关键参数

电压传输特性:

VCC, Operating Voltage(工作电压):确保逻辑器件可以正常工作的供电电压范围。

输入和输出特性:

IOH, Output High Drive Current(高电平输出电流):输出为高电平时,提供给外接负载的输出电流

IOL, Output Low Drive Current (低电平输出电流):输出为低电平时候,外接负载提供的电流(电流方向从负载流向IC)

输入和输出的高/低电平:

Input Voltages(输入电压)

VIH, Minimum Input High Level(输入高电平):能被逻辑器件判断为逻辑“高”的最小的输入电压

VIL, Maximum Input Low Level(输入低电平):能被逻辑器件判断为逻辑“低”的最大的输入电压

Output Voltage(输出电压)

VOH, Output High Voltage Level(输出高电平):能被逻辑器件判断为逻辑“高”的最小的输出电压

VOL, Output Low Voltage Level(输出低电平):能被逻辑器件判断为逻辑“低”的最大的输出电压

图11 CMOS逻辑电平(左)/TTL逻辑电平(右)

噪声容限:

高电平噪声容限VNH:

低电平噪声容限VNL:

图12 噪声容限示意图

带负载能力:

门电路的扇入数取决于它的输入端的个数,例如一个3输入端的与非门,其扇入数NI=3。门电路的扇出数是指其在正常工作情况下,所能驱动同类门电路的最大数目(反映了门电路的带负载能力)。

带拉电流负载:

带灌电流负载:

图13 驱动与负载之间的关系

驱动和负载之间应该满足的关系:

VOH ≥ VIH, VOL ≤ VIL

IOH or IOL ≥ I1 + I2 + …… + In

输出延迟时间:

传输延迟时间是表征门电路开关速度的参数,它说明门电路在输入脉冲(波形)的作用下,其输出波形相对于输入波形延迟了多长时间。

导通延迟时间tPHL: 从输入波形上升沿的中点到输出波形下降沿的中点所经历的时间。

截止延迟时间tPLH: 从输入波形下降沿的中点到输出波形上升沿的中点所经历的时间。

图14 CMOS电路传输延时时间

逻辑门的平均传输延迟时间tpd:

数字电路中时延的主要表现为竞争冒险现象,现代逻辑电路设计需要考虑逻辑器件时延的影响,就应该对其及产生的时序问题进行分析。逻辑电路的延迟本质上是一系列逻辑门电路延迟的叠加。

在交换机选型设计中应考虑逻辑门的输入输出时延的问题时,结合信号速率和应用场景分析,如5MHZ的LED点灯信号,周期为200ns,74LV164(NXP)在3.3V工作状态下tPD为29ns,需要结合CP与Qn,和MR与Qn的建立时间和保持时间去考虑,实测时延。

对于工作在标准模式下的IIC,100KHz的周期为1us,逻辑门电路或者缓冲器的延时一般为2~23ns,则不需要考虑时延的问题。

注:当逻辑器件叠加使用,时延去到同个数量级时,也需要去考虑测试时延。

功耗:

功耗是门电路的重要参数之一。功耗有静态功耗和动态功耗之分。所谓静态功耗指的是当电路的输出没有状态转换时的功耗。CMOS电路在输出发生状态转换时的功耗称为动态功耗。CMOS电路的动态功耗与转换频率和电源电压的平方成正比。当工作频率比较高时,CMOS门的功耗可能会超过TTL电路。在设计CMOS 电路时,尽量选用低电源电压器件,例如3.3V供电电源74LVC系列或1.8V供电电源74AUC系列,以降低功率损耗。

功耗-延时积: