Quartus II运行综合时警告Warning 15714

一、出现问题

第一次使用Quartus II编译项目代码时,软件报告如下警告:

意思就是管脚有不完整的I/O分配。

二、问题解决

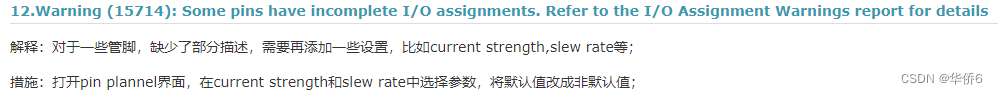

我当时也没多想,直接百度。看到一篇回答如下:

看到这里我愣了一下,这些current是啥意思啊?怎么给引脚设置这些参数啊?这些参数怎么选定啊?不知道。突然意识到我根本就没有分配引脚!于是,我赶紧返回去看警告,捕捉到一个关键数字31:

这不是我总的输入和输出引脚数目吗?顿时恍然大悟,嗯~回去分配引脚了。

三、总结

我在这里是由于粗心大意忘记分配引脚才导致这个警告,也不排除有些朋友分配了引脚还是遇到这个警告,那就要考虑是不是没有设置相关参数了。

参考文献:

- [Warning 15714——geekite]