目录

问题现象

问题解决

问题现象

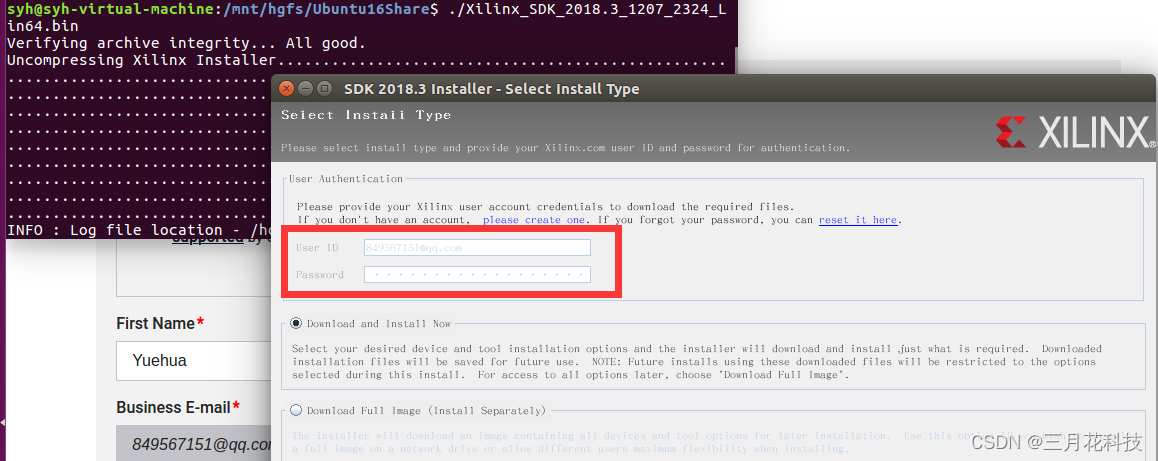

在Linux系统安装Xilinx_SDK时,第二步需要输入Xilinx的账户名和密码,如果没有账户名和密码,可以点击界面中的”please create one“来创建。但问题就出在正确创建Xilinx用户后依然无法正常安装软件,报错如下

出现这个问题的根本原因是注册Xilinx账户还有未填写的用户信息。解决方法如下:

问题解决

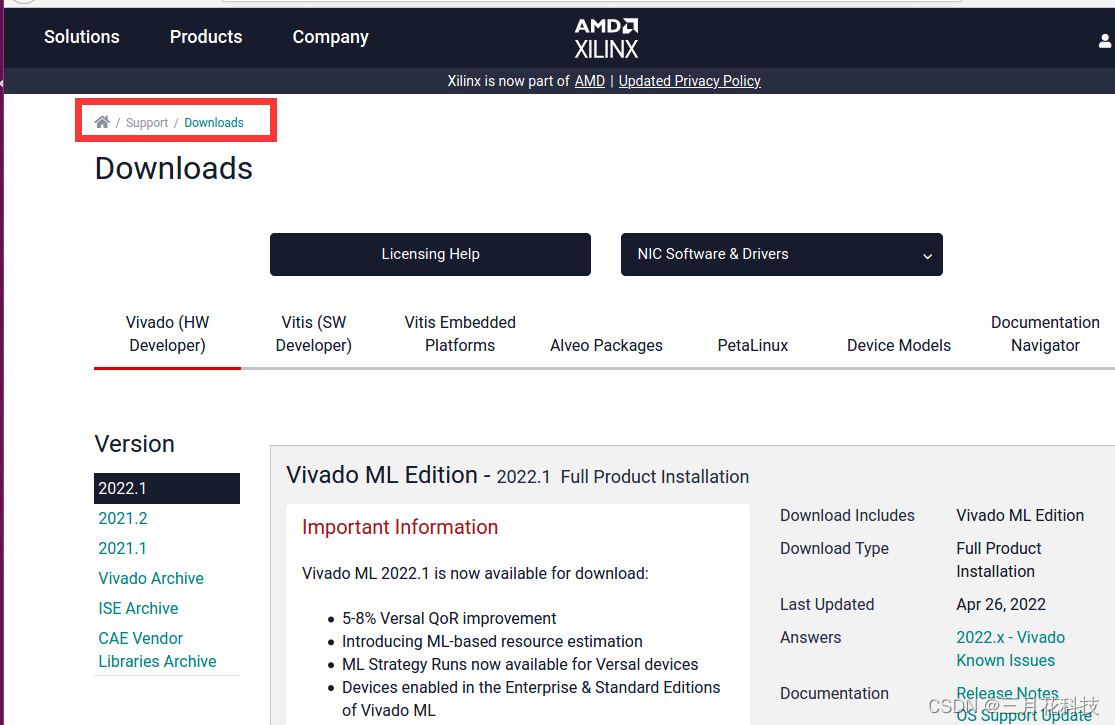

用注册的Xilinx账号登陆Xilinx官方网站,然后进入下载站如下图:

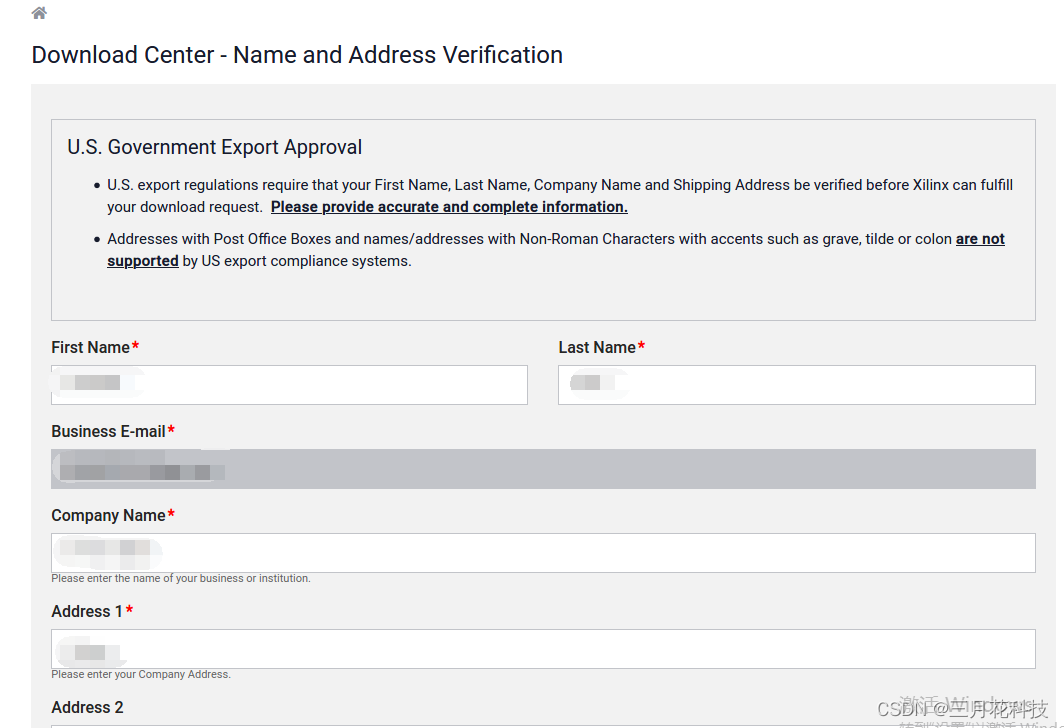

随便找个东西下载,如果账户少填写了东西,会提示填写信息,界面如下:

将这些信息填写好并提交后,若选择的软件可以正常下载,证明Xilinx账户缺失的个人信息填写完成。

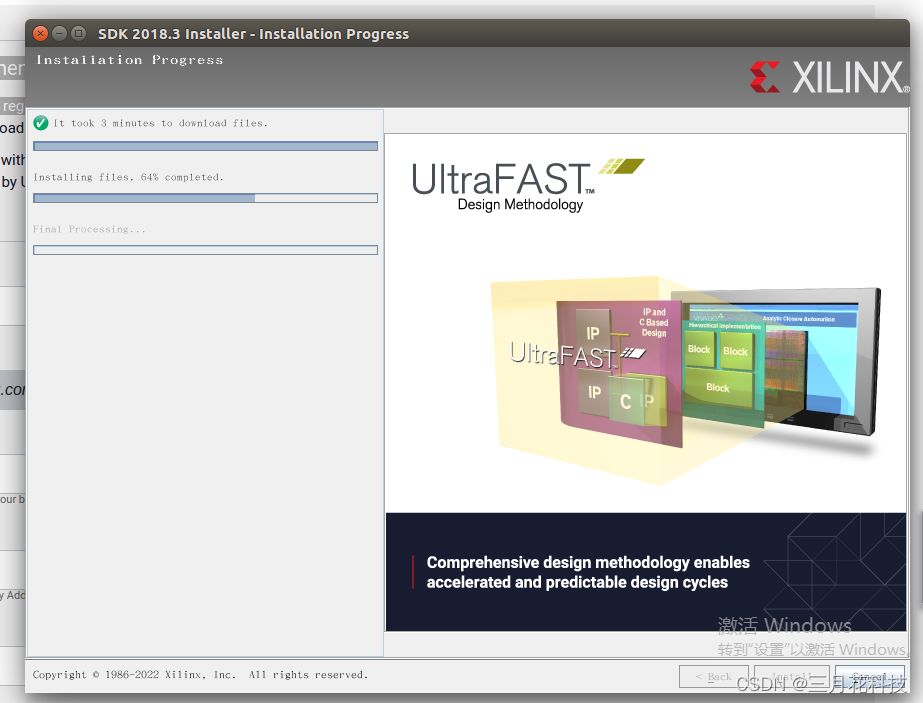

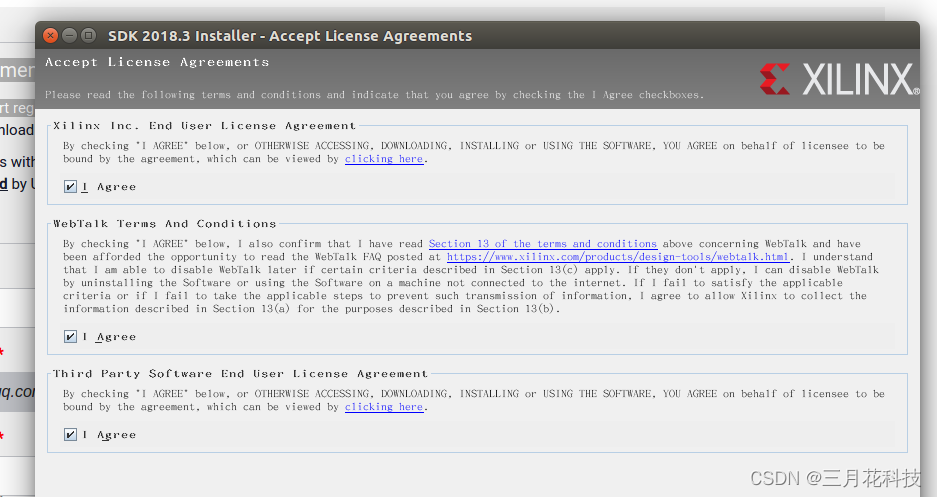

此时,回到Xilinx_SDK的安装界面,就可以使用注册的Xilinx账户正常安装了,成功进入到第三页如下图;

选择好需要安装的内容和路径后就可以正常安装了,如下图所示: