目录

建立工程

添加顶层

模块1

模块2

添加约束文件

编辑时钟约束

打开布线设计

代码代表的含义

时序报告

进行时序分析

Summary:包含了汇总的信息量

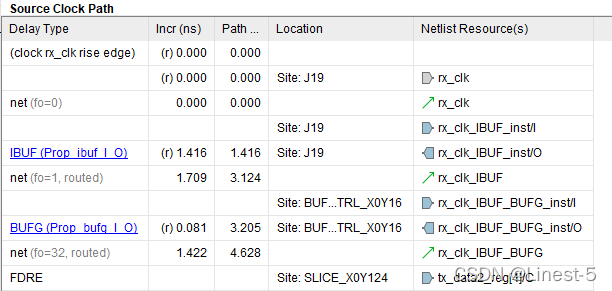

Source Clock Path:这部分是表示Tclk1的延时细节

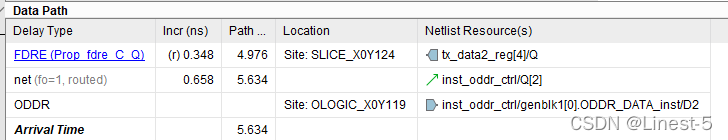

Data Path:数据路径的延时

往期系列博客:

建立工程

在之前进行了时序分析的理论部分的学习,接下来就开始真正在实验工程去实操,看看在Vivado中时序约束以及分析是如何进行操作的,同样实操也可以加深理论知识的理解,理论与实际相结合。

本次上手实操关于建立时间保持时间的时序分析和约束,实验工程源码和工程项目在资源可以下载。

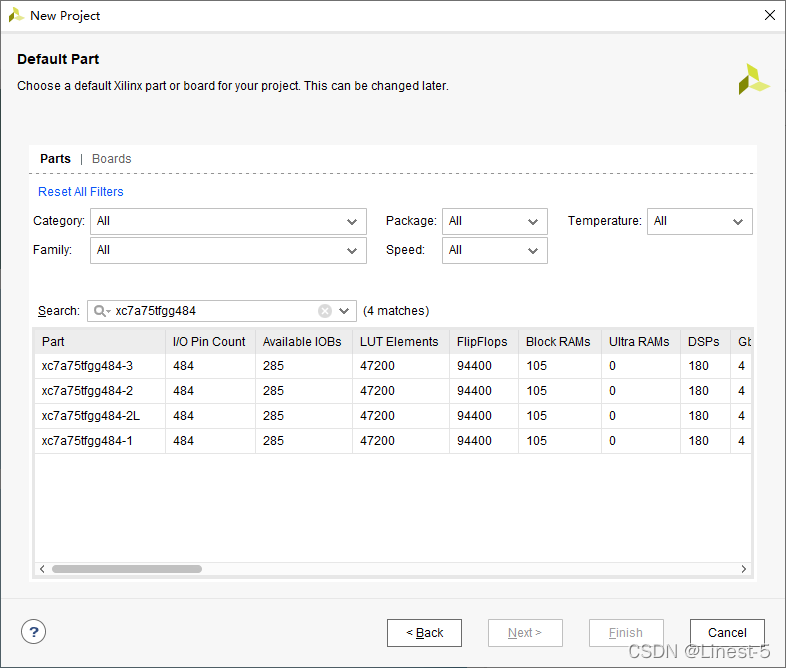

新建一个实验工程,命名为timing,选择自己的板子的型号,我这里用的是xc7a75tfgg484-2型号的板子,点击创建即可。

添加顶层

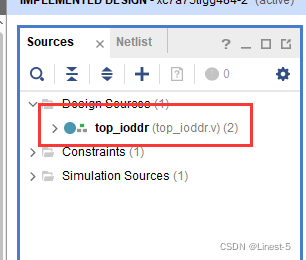

添加一个顶层文件命名为top_ioddr,将事先存在的.v文件加入即可

module top_ioddr( input wire rx_clk, input wire rx_ctrl, input wire [3:0] rx_dat, //tx output wire tx_clk, output wire [3:0] tx_d, output wire tx_dv);wire rst;wire rx_clk_90;wire rx_en;wire [7:0] rx_data;reg tx_en1,tx_en2;reg [7:0] tx_data1,tx_data2;assign rst =0;assign rx_clk_90 = rx_clk;always @(posedge rx_clk_90 or posedge rst) beginif (rst == 1'b1) begintx_data1 <= 'd0;endelse if (rx_en == 1'b1) begintx_data1 <= rx_data+ rx_data -1;endendalways @(posedge rx_clk_90 or posedge rst) beginif (rst == 1'b1) begintx_data2 <= 'd0;endelse if (tx_en1 == 1'b1) begintx_data2 <= tx_data1+ tx_data1 -5;endendalways @(posedge rx_clk_90 ) begintx_en1 <= rx_en;endalways @(posedge rx_clk_90 ) begintx_en2 <= tx_en1;endiddr_ctrl inst_iddr_ctrl(.rx_clk_90 (rx_clk_90),.rst (rst),.rx_dat (rx_dat),.rx_ctrl (rx_ctrl),.rx_en (rx_en),.rx_data (rx_data));oddr_ctrl inst_oddr_ctrl(.sclk (rx_clk_90),.tx_dat (tx_data2),.tx_en (tx_en2),.tx_c (rx_clk_90),.tx_data (tx_d),.tx_dv (tx_dv),.tx_clk (tx_clk));endmodule

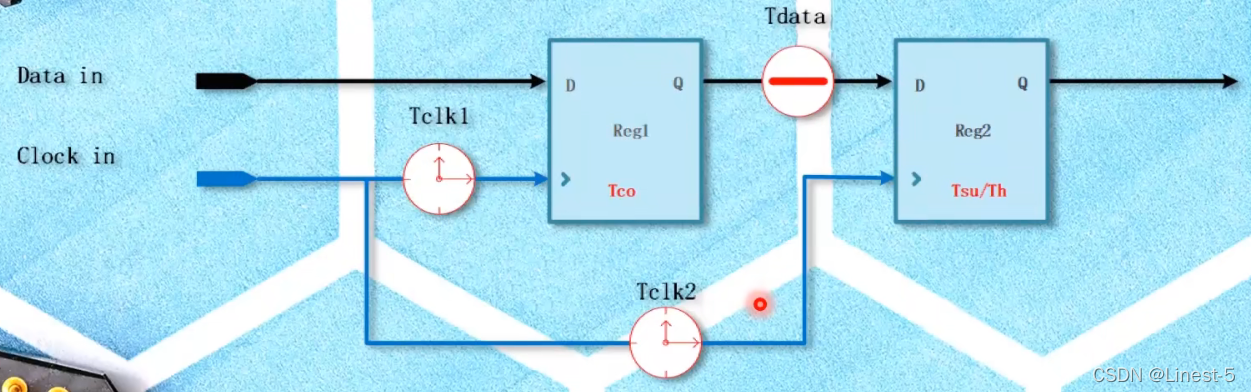

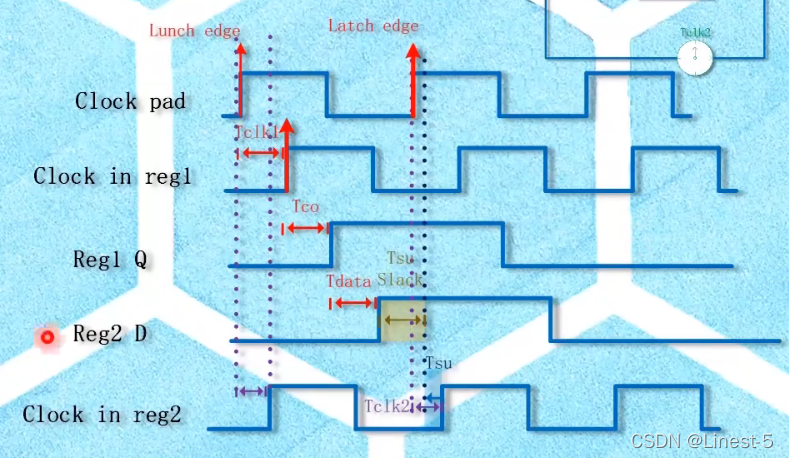

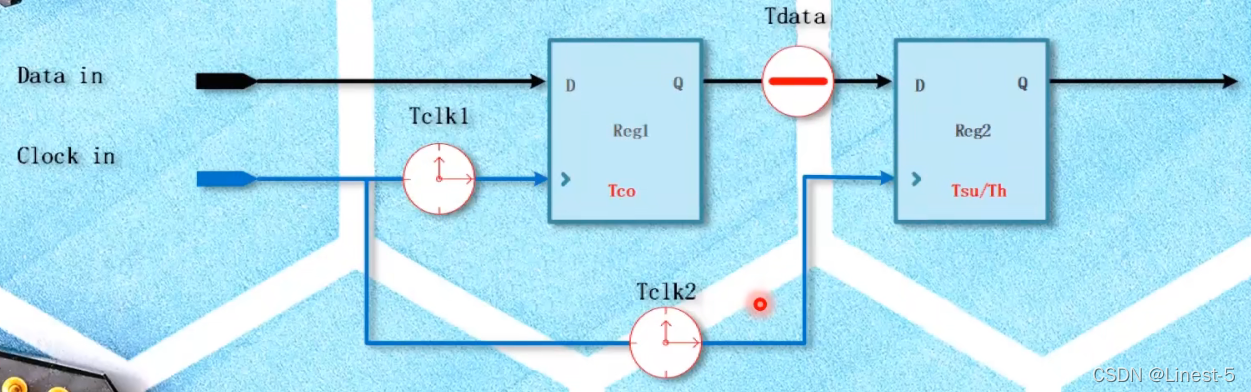

其代码的大致实现的工程就是在之前的时序文章讲到的两拍寄存器的操作,类似下图的模型结构。

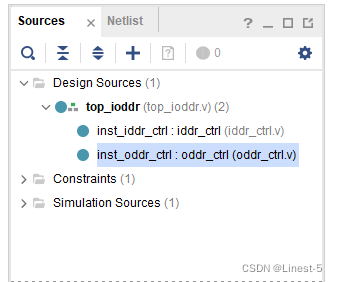

另外同样的操作添加顶层下面的两个子模块

模块1

moduleoddr_ctrl(

inputwiresclk,

inputwire[7:0]tx_dat,

inputwiretx_en,

inputwiretx_c,//相移时钟

outputwire[3:0]tx_data,

outputwiretx_dv,

outputwiretx_clk

);

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

)

ODDR_DV_inst (

.Q(tx_dv), // 1-bit DDR output

.C(sclk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(tx_en), // 1-bit data input (positive edge)

.D2(tx_en), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

)

ODDR_CLK_inst (

.Q(tx_clk), // 1-bit DDR output

.C(tx_c), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(1'b1), // 1-bit data input (positive edge)

.D2(1'b0), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

genvar j;

generate

for(j=0;j<4;j=j+1) begin

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

)

ODDR_DATA_inst (

.Q(tx_data[j]), // 1-bit DDR output

.C(sclk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(tx_dat[j]), // 1-bit data input (positive edge)

.D2(tx_dat[j+4]), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

end

endgenerate

endmodule

模块2

moduleoddr_ctrl(

inputwiresclk,

inputwire[7:0]tx_dat,

inputwiretx_en,

inputwiretx_c,//相移时钟

outputwire[3:0]tx_data,

outputwiretx_dv,

outputwiretx_clk

);

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

)

ODDR_DV_inst (

.Q(tx_dv), // 1-bit DDR output

.C(sclk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(tx_en), // 1-bit data input (positive edge)

.D2(tx_en), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

)

ODDR_CLK_inst (

.Q(tx_clk), // 1-bit DDR output

.C(tx_c), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(1'b1), // 1-bit data input (positive edge)

.D2(1'b0), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

genvar j;

generate

for(j=0;j<4;j=j+1) begin

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

)

ODDR_DATA_inst (

.Q(tx_data[j]), // 1-bit DDR output

.C(sclk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(tx_dat[j]), // 1-bit data input (positive edge)

.D2(tx_dat[j+4]), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

end

endgenerate

endmodule

最终得到的设计层如下图,模块的命名可以自己定。

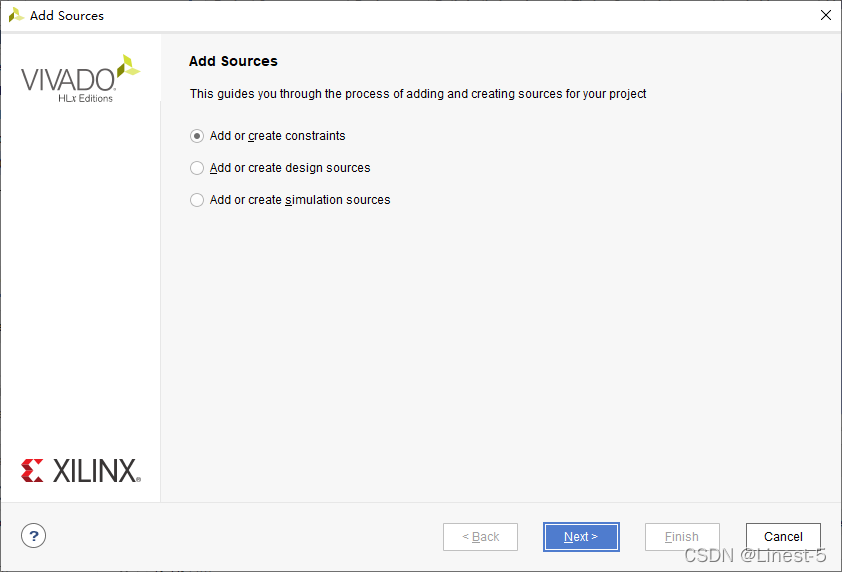

添加约束文件

点击加号添加constrains文件

约束代码如下,不同板子的管脚以及电压可能不一样,看原理图就可以分配管脚、电压。

set_property IOSTANDARD LVCMOS33 [get_ports rx_clk]set_property PACKAGE_PIN J19 [get_ports rx_clk]set_property PACKAGE_PIN H22 [get_ports rx_ctrl]set_property IOSTANDARD LVCMOS33 [get_ports rx_ctrl]set_property PACKAGE_PIN K22 [get_ports {rx_dat[0]}]set_property PACKAGE_PIN K21 [get_ports {rx_dat[1]}]set_property PACKAGE_PIN J22 [get_ports {rx_dat[2]}]set_property PACKAGE_PIN J20 [get_ports {rx_dat[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[0]}]set_property PACKAGE_PIN M18 [get_ports tx_dv]set_property IOSTANDARD LVCMOS33 [get_ports tx_dv]set_property PACKAGE_PIN K18 [get_ports tx_clk]set_property IOSTANDARD LVCMOS33 [get_ports tx_clk]set_property PACKAGE_PIN M22 [get_ports {tx_d[0]}]set_property PACKAGE_PIN L18 [get_ports {tx_d[1]}]set_property PACKAGE_PIN L19 [get_ports {tx_d[2]}]set_property PACKAGE_PIN L20 [get_ports {tx_d[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[0]}]

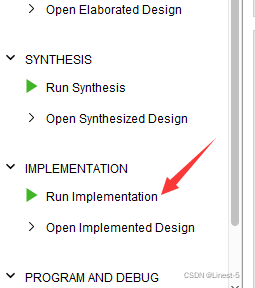

点击左侧菜单栏的布局布线,由于工会曾比较小,大概三分钟左右就可以完成。

编辑时钟约束

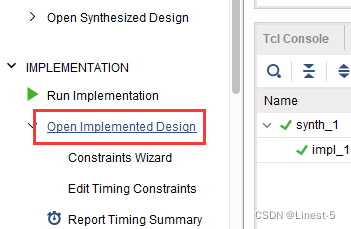

打开布线设计

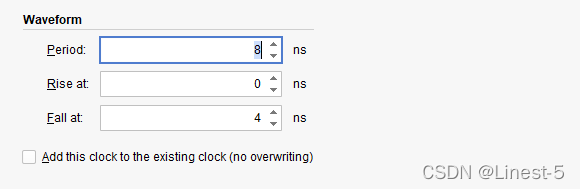

然后点击编辑时序约束,添加我们所想要的时序约束,在clock中选择创建时钟,注意:如果时钟由PLL生成,这里就不需要添加时钟的约束,因为它会自动生成约束,双击打开create clock,添加一个周期为8ns的时钟,令其一开始就为高电平,如下图设置,设置完点击ok即可。

时钟命名完成后,选择它所对应的时钟,再点击set,最后ctrl+s保存即可。

这时候再打开xdc文件,就可以看到多出一行约束代码,这条约束就是刚刚设置的时钟约束。

代码代表的含义

创建一个名为rx_clk的时钟,周期为8ns,再0ns时刻为上升沿,再4ns时刻为下降沿,此时钟约束对应名为rx_clk的端口。

并且,由于约束文件发生了变化,因此需要重新生成比特流文件,然后重新打开此界面。

set_property IOSTANDARD LVCMOS33 [get_ports rx_clk]set_property PACKAGE_PIN J19 [get_ports rx_clk]set_property PACKAGE_PIN H22 [get_ports rx_ctrl]set_property IOSTANDARD LVCMOS33 [get_ports rx_ctrl]set_property PACKAGE_PIN K22 [get_ports {rx_dat[0]}]set_property PACKAGE_PIN K21 [get_ports {rx_dat[1]}]set_property PACKAGE_PIN J22 [get_ports {rx_dat[2]}]set_property PACKAGE_PIN J20 [get_ports {rx_dat[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {rx_dat[0]}]set_property PACKAGE_PIN M18 [get_ports tx_dv]set_property IOSTANDARD LVCMOS33 [get_ports tx_dv]set_property PACKAGE_PIN K18 [get_ports tx_clk]set_property IOSTANDARD LVCMOS33 [get_ports tx_clk]set_property PACKAGE_PIN M22 [get_ports {tx_d[0]}]set_property PACKAGE_PIN L18 [get_ports {tx_d[1]}]set_property PACKAGE_PIN L19 [get_ports {tx_d[2]}]set_property PACKAGE_PIN L20 [get_ports {tx_d[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {tx_d[0]}]create_clock -period 8.000 -name rx_clk -waveform {0.000 4.000} [get_ports rx_clk]

时序报告

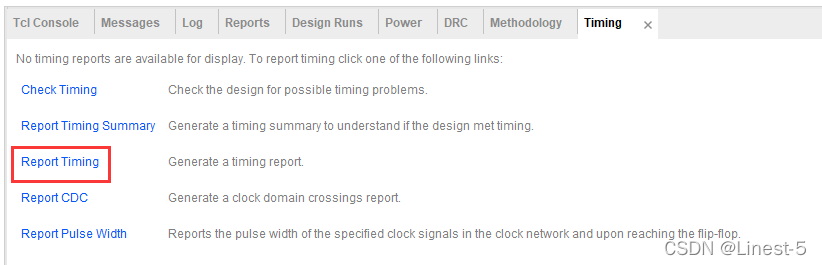

点击report timing,可以打印时序报告

选择100条路径,每条路径设置一个结点,点击ok

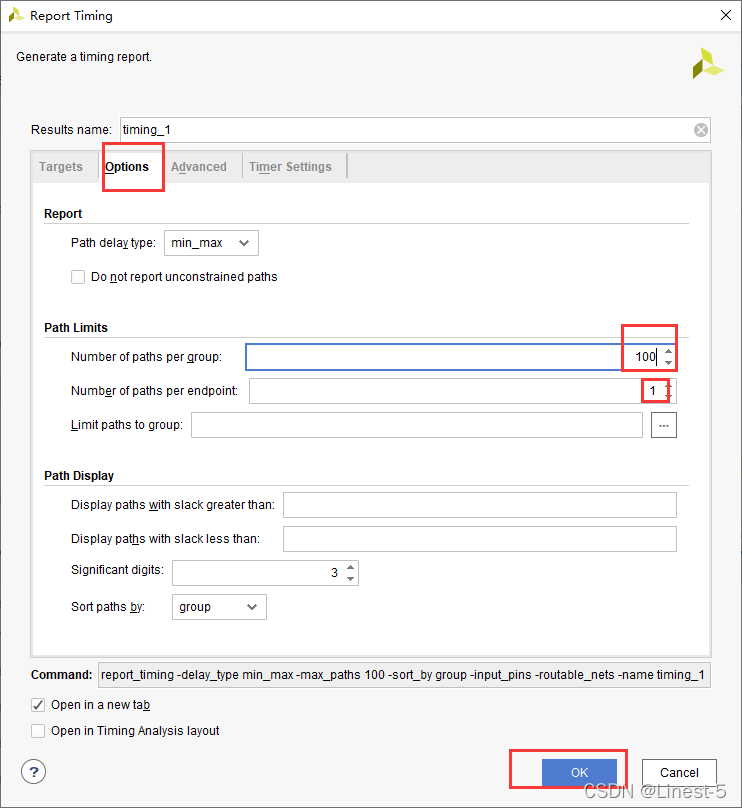

这时候就会有时序的报告

slack:表示建立时间的余量

level:逻辑延时等级,这里1就表示你可能在语句中加了if条件语句、case语句等逻辑语句

fanout:表示从这一点连接到了几个目的端点,fanout = 1就表示连接了1个目的端点

from to:表示是哪两者之间的时序

以及后面的有总的延时、逻辑延时等等

双击点开想要看的路径细节(这里点开路径42为例)

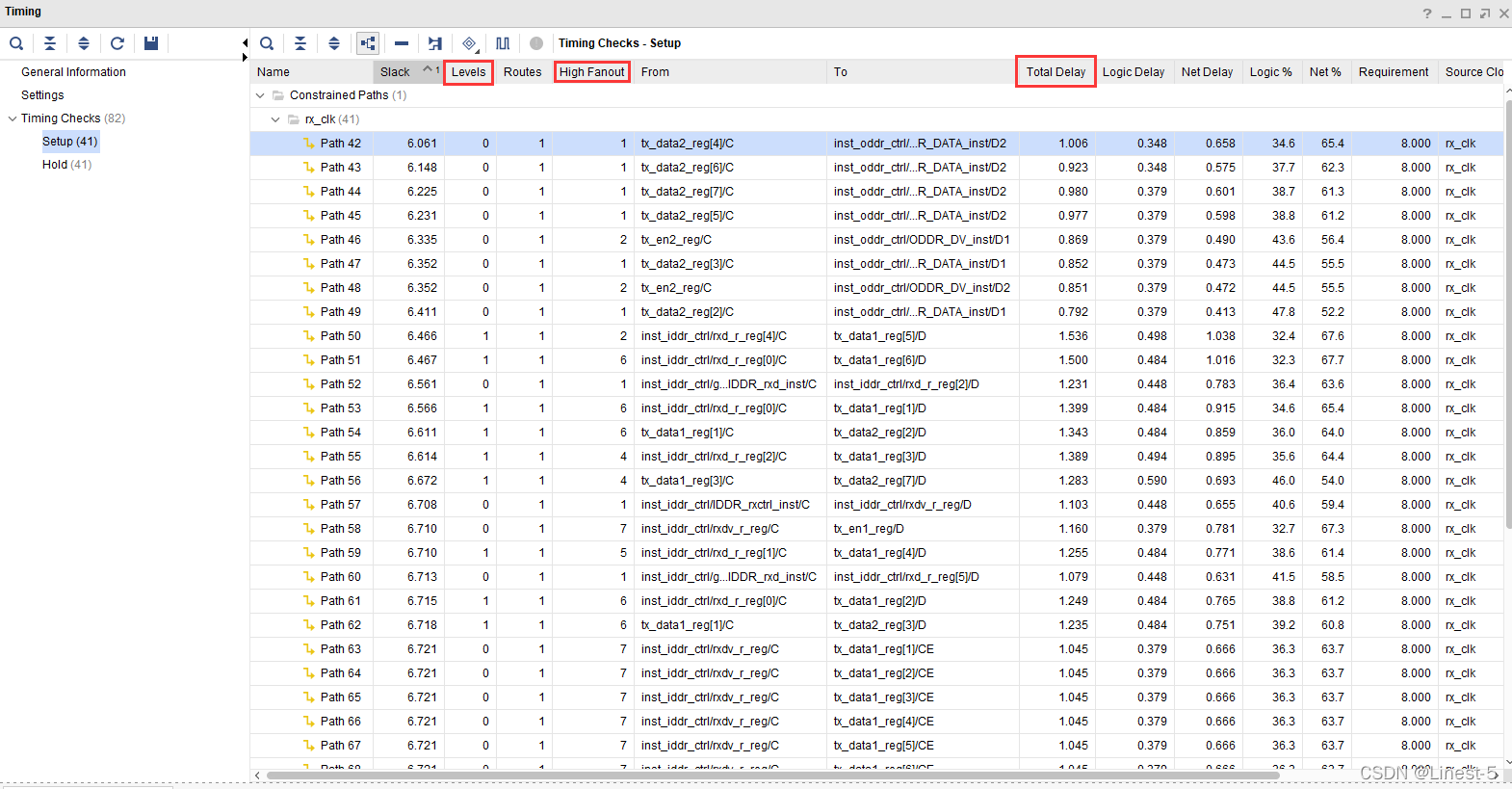

进行时序分析

对应着数据和时钟的时序图以及两级寄存器分析。

Summary:包含了汇总的信息量

Source Clock Path:这部分是表示Tclk1的延时细节

从时钟的上升沿clock rx_clk rise edge到rx_clk_IBUF_inst/I 这部分表示从源时钟到IBUF走过的延时,每一路时钟都须经过IBUF,IBUF起到缓冲的作用,增加时钟的驱动力,从时序报告里看,这部分是没有延时的。

rx_clk_IBUF_inst/I ->rx_clk_IBUF_inst/O:从IBUF的输入到输出这部分是有延时的,延时是1.416ns。

rx_clk_IBUF_inst/O ->rx_clk_IBUF:这部分就是从IBUF的输出到rx_clk_IBUF部分的net,也就是布线延迟,延时是1.709。

rx_clk_IBUF_BUFG_inst/I ->rx_clk_IBUF_BUFG_inst/O,从BUFG输入到输出的延时。

最后的net布线延时1.422ns。

这些一起加起来的延时总和就是Tclk1的延时时间。

Data Path:数据路径的延时

Prop fdre C Q:这部分是时钟端到寄存器的Q端,也就是Tco,这部分的延时是0.348ns。

net:PCB布线延时0.658ns。

加上之前的Tck1,这部分总和延时就是数据到达的时间总和。

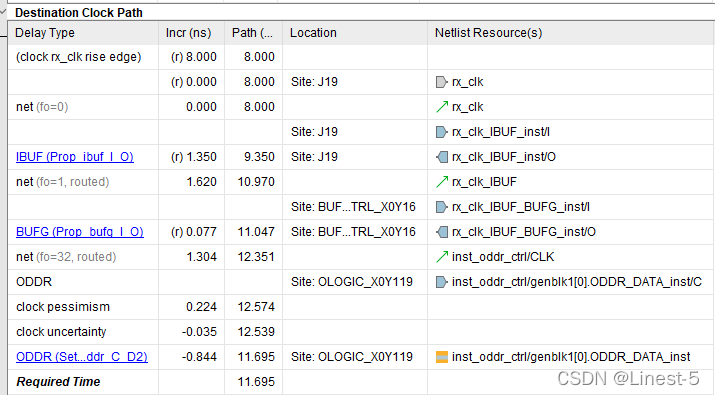

Destination Clock Path:数据所被要求到达的时间。

clock rx_clk rise edge:一个时钟周期的延时8ns。

rx_clk_IBUF_inst/I ->rx_clk_IBUF_inst/O:从IBUF的输入到输出这部分是有延时的,延时是1.350ns。

net:布线延时1.620ns。

rx_clk_IBUF_BUFG_inst/I ->rx_clk_IBUF_BUFG_inst/O,从BUFG输入到输出的延时0.077ns。

net:布线延时1.304ns。

clock pessimism:时钟的悲观度

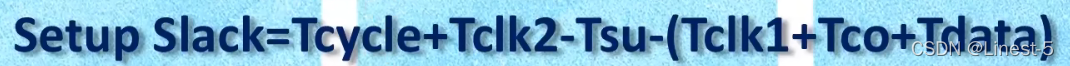

可以看到上面的建立时间余量的公式,为了能在最糟糕的情况下建立时间能够满足,我们就让Tclk1尽可能的大,Tclk2尽可能的小,这样setup slack就会处于最小值,如果在此时最坏的情况下都能够满足建立时间按的要求,那么在其他任何情况下,都能够满足要求。

可以看到前面同样是rx_clk_IBUF_inst/I ->rx_clk_IBUF_inst/O和rx_clk_IBUF_BUFG_inst/I ->rx_clk_IBUF_BUFG_inst/O,这两条路径是时钟和数据的共同路径,但是数据到达的路径和时钟的路径所经历这段延时却是不一样的,而时钟的悲观度正是体现在这里,时钟的悲观度的值就是这两者的差值。并且并不是单一路的差值,它是综合整个系统给出的悲观度。

clock uncertainty:这个是时钟的不确定性,这个是芯片所决定的,无法计算。

ODDR(set ddr C D2):这个是最小建立时间,所以是减去。

可以验证用数据所需要到达的时间减去数据实际到达的时间就是前面summary的slack。

这个实验工程是看建立时间的时序,类似的操作可以看保持时间的时序分析。

往期系列博客:

【Xilinx Vivado时序分析/约束系列1】FPGA开发时序分析/约束-寄存器间时序分析

【Xilinx Vivado时序分析/约束系列2】FPGA开发时序分析/约束-建立时间

【Xilinx Vivado时序分析/约束系列3】FPGA开发时序分析/约束-保持时间