奇数分频

1、奇数分频介绍

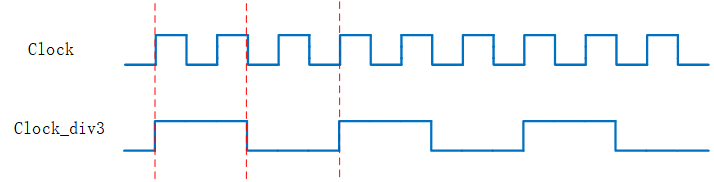

奇数分频(2N+1),以三分频(N=1)为例,三分频即分频后的时钟半周期(周期)是原时钟半周期(周期)的3倍宽度。

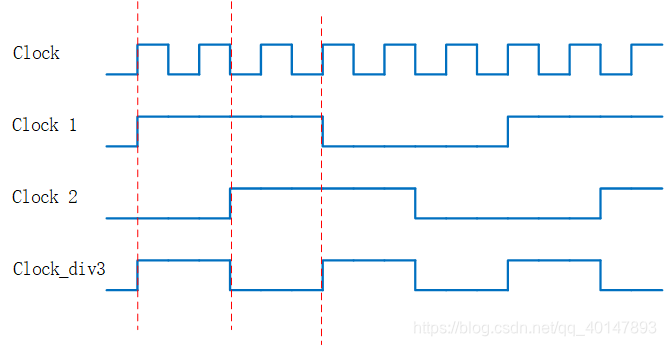

偶数分频我们只需要借助原时钟的上升沿或者下降沿进行计数分频,但是要实现奇数分频我们就要同时利用原时钟的上升沿和下降沿。可以通过原时钟的上升沿和下降沿计数产生clk1和clk2,再通过clk1和clk2的关系实现奇数分频。这种关系可以是或、与、异或,详细如下所述。

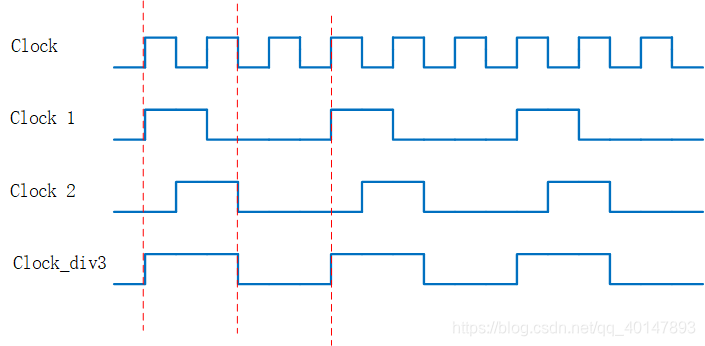

2、通过时钟 相或 实现奇数分频

原时钟clk通过上升沿和下降沿计数产生时钟clk1和clk2,clk1和clk2 相或 产生clk三分频的clk_div3时钟。

clk1:原时钟clk的上升沿产生。

clk2:原时钟clk的下降沿产生。

clk1和clk2特征:

3分频:高电平:低电平 = 1:2。

2N+1分频:高电平:低电平 = N:N+1。

代码:

//时钟 相或

module top

(

input clk_150m,

input rst_n,

output clk_div3

);

reg [3:0] cnt_1;//上升沿计数

reg [3:0] cnt_2;//下降沿计数

reg clk_1;

reg clk_2;

assign clk_div3 = clk_1 | clk_2;

always@(posedge clk_150m or negedge rst_n)

begin

if(!rst_n)

begin

cnt_1 <= 4'd0;

clk_1 <= 1'b0;

end

else

begin

cnt_1 <= (cnt_1 == 4'd2)?4'd0:cnt_1+4'd1;

clk_1 <= (cnt_1 == 4'd1)?1'b1:1'b0;

end

end

always@(negedge clk_150m or negedge rst_n)

begin

if(!rst_n)

begin

cnt_2 <= 4'd0;

clk_2 <= 1'b0;

end

else

begin

cnt_2 <= (cnt_2 == 4'd2)?4'd0:cnt_2+4'd1;

clk_2 <= (cnt_2 == 4'd1)?1'b1:1'b0;

end

end

endmodule

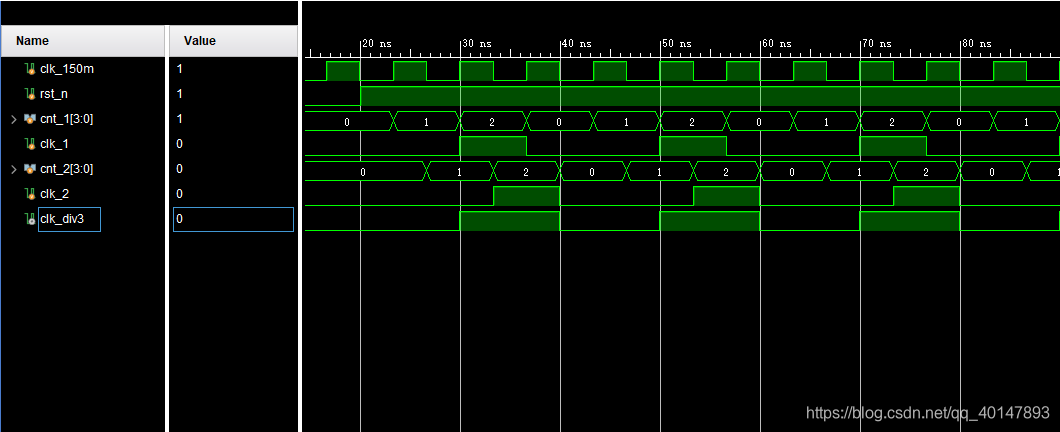

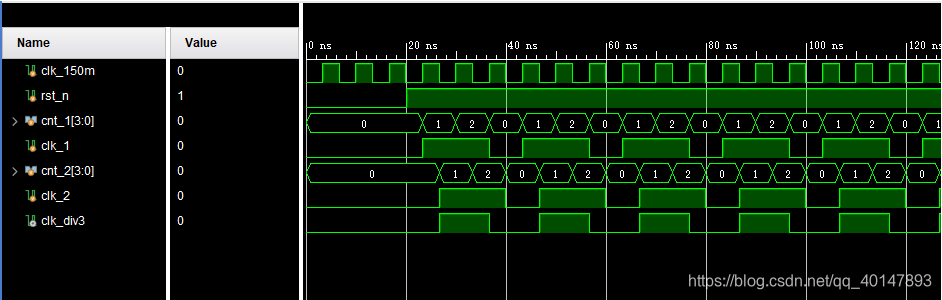

仿真波形:

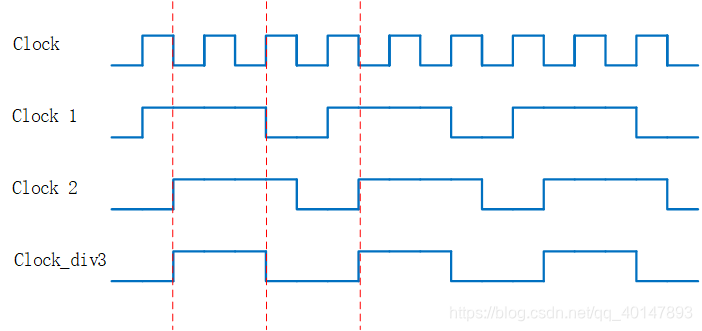

3、通过时钟 相与 实现奇数分频

原时钟clk通过上升沿和下降沿计数产生时钟clk1和clk2,clk1和clk2 相与 产生clk三分频的clk_div3时钟。

clk1:原时钟clk的上升沿产生。

clk2:原时钟clk的下降沿产生。

clk1和clk2特征:

3分频:高电平:低电平 = 1:2。

2N+1分频:高电平:低电平 = N+1:N。

代码:

//时钟 相与

module top

(

input clk_150m,

input rst_n,

output clk_div3

);

reg [3:0] cnt_1;//上升沿计数

reg [3:0] cnt_2;//下降沿计数

reg clk_1;

reg clk_2;

assign clk_div3 = clk_1 & clk_2;

always@(posedge clk_150m or negedge rst_n)

begin

if(!rst_n)

begin

cnt_1 <= 4'd0;

clk_1 <= 1'b0;

end

else

begin

cnt_1 <= (cnt_1 == 4'd2)?4'd0:cnt_1+4'd1;

clk_1 <= (cnt_1 <= 4'd1)?1'b1:1'b0;

end

end

always@(negedge clk_150m or negedge rst_n)

begin

if(!rst_n)

begin

cnt_2 <= 4'd0;

clk_2 <= 1'b0;

end

else

begin

cnt_2 <= (cnt_2 == 4'd2)?4'd0:cnt_2+4'd1;

clk_2 <= (cnt_2 <= 4'd1)?1'b1:1'b0;

end

end

endmodule

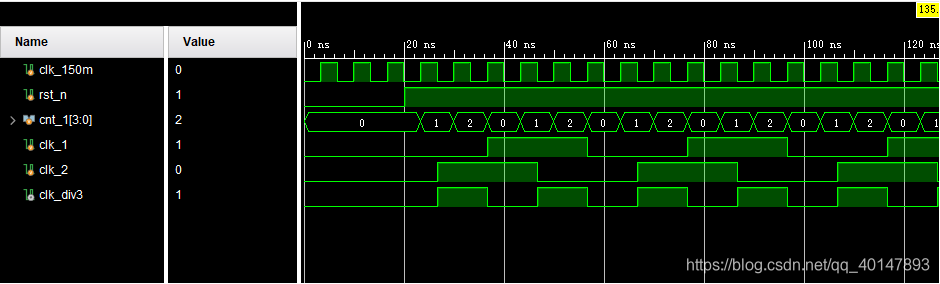

仿真波形:

4、通过时钟 相异或 实现奇数分频

原时钟clk通过上升沿和下降沿计数产生时钟clk1和clk2,clk1和clk2 相异或 产生clk三分频的clk_div3时钟。

clk1:原时钟clk的上升沿产生。

clk2:原时钟clk的下降沿产生。

clk1和clk2特征:

3分频:clk1以原时钟clk的3个周期为单位翻转,clk2在clk1时钟的中间点发生翻转。

2N+1分频:clk1以原时钟clk的2N+1个周期为单位翻转,clk2在clk1时钟的中间点发生翻转。

代码:

//时钟 相异或

module top

(

input clk_150m,

input rst_n,

output clk_div3

);

reg [3:0] cnt_1;//上升沿计数

reg clk_1;

reg clk_2;

assign clk_div3 = clk_1 ^ clk_2;

always@(posedge clk_150m or negedge rst_n)

begin

if(!rst_n)

begin

cnt_1 <= 4'd0;

clk_1 <= 1'b0;

end

else

begin

cnt_1 <= (cnt_1 == 4'd2)?4'd0:cnt_1+4'd1;

clk_1 <= (cnt_1 == 4'd2)?~clk_1:clk_1;

end

end

always@(negedge clk_150m or negedge rst_n)

begin

if(!rst_n)

begin

clk_2 <= 1'b0;

end

else

begin

clk_2 <= (cnt_1 == 4'd1)?~clk_2:clk_2;

end

end

endmodule

仿真波形:

5、测试代码

测试代码:

module test;

reg clk_150m;

reg rst_n;

wire clk_div3;

top u1

(

.clk_150m(clk_150m),

.rst_n(rst_n),

.clk_div3(clk_div3)

);

initial

begin

clk_150m = 0;

rst_n = 0;

#20;

rst_n = 1;

end

always # 3.3333 clk_150m = ~clk_150m;

endmodule

★★★如有错误,欢迎指导!!!