目录

1 配置空间

1.1 PCI Power Management Capability Structure

1.2 PCI Express Capability Structure

2 扩展配置空间

2.1 Virtual Channel Extended Capability

2.2 PCIe DVSEC for CXL Device

2.3 GPF DVSEC for CXL Devices

2.4 PCIe DVSEC for Flex Bus Port

2.5 Register Locator DVSEC

由于CXL协议基于PCIe协议,因此CXL配置空间大小、布局与PCIe相同。

CXL 2.0 Device配置空间一共4KB,由配置空间(0x000~0x0FF)和扩展配置空间(0x100~0xFFF)组成,如下所示。

- 配置空间,通常由Header和若干个Capability组成;

- 扩展配置空间,通常由若干个扩展Capability组成。

1 配置空间

CXL 2.0 Device属于EndPoint,因此Header类型为Type0,Header长度固定为64B。

在Offset:0x00~0x3F,表示Type0 Header,如下所示:

在Offset:0x40~0xFF,表示Device具备的Capabilities。这里仅列出对于所有Device来说,必须具备的Capability,如下所示:

- PCI Power Management Capability Structure

- PCI Express Capability Structure

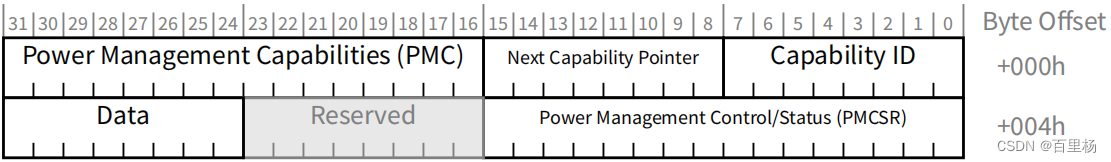

1.1 PCI Power Management Capability Structure

PCI Power Management Capability寄存器对于PCI总线来说是可选的,但是对于PCIe总线来说则是强制的。此Capability占用8B,如下所示:

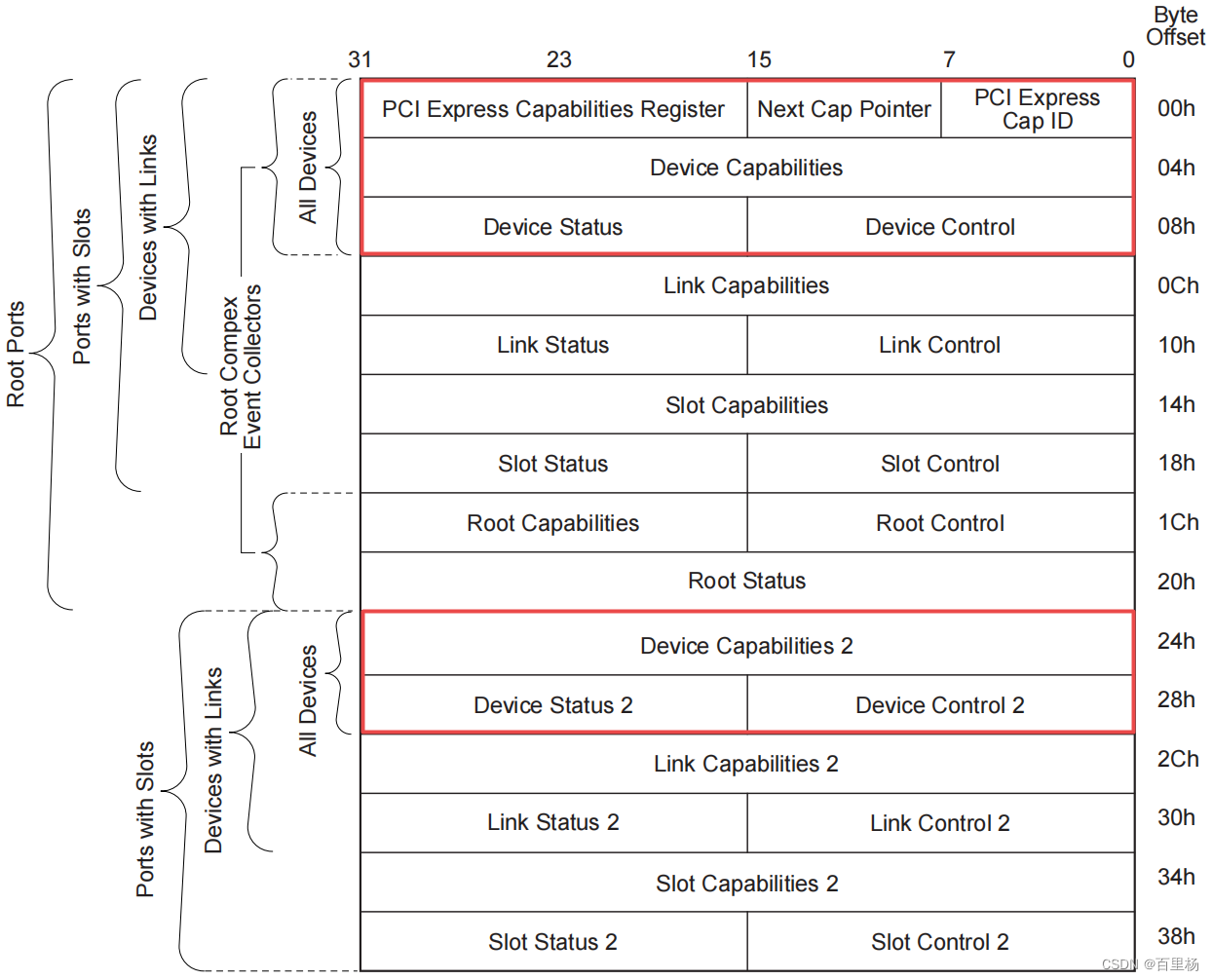

1.2 PCI Express Capability Structure

PCI Express Capability Structure占用60B,如下所示:

但是以上这些寄存器, 仅有红框标注的寄存器才是每个设备必须具备的,它们主要包括:Device Capabilities、Device Status、Device Control等。

对于Devices with Links,还需要具备Link系列寄存器,这些寄存器,对于每个Device来说并不是必须的,属于可选。

2 扩展配置空间

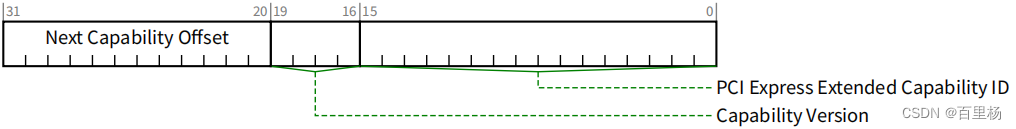

扩展配置空间中的Extended Capability总是从偏移量0x100开始,并且每个Extended Capability带有一个 PCI Express Extended Capability header。如果没有任何Extended Capability,则其Next Capability为0。

PCI Express Extended Capability header,占用4B,如下所示:

在Offset:0x100~0xFFF,表示Device具备的Extended Capabilities。这里仅列出对于所有Device来说,必须具备的Extended Capabilities,如下所示:

- Virtual Channel Extended Capability

好了,以上介绍的只是PCIe协议中,在这4KB空间中定义的Capability与Extended Capability。而CXL协议还定义了一些Extended Capability,它们是基于PCIe的Designated Vendor-Specific Extended Capability (DVSEC Capability)来实现的。

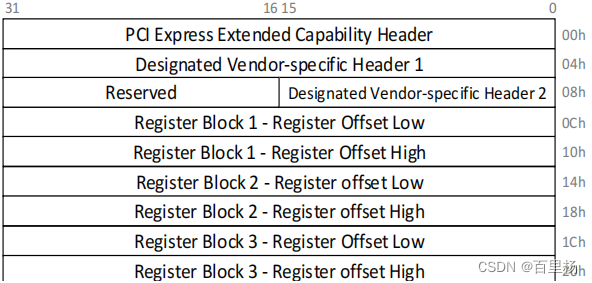

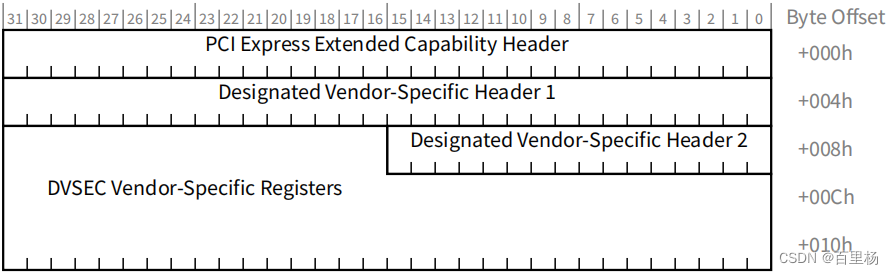

DVSEC Capability的基本结构,如下所示:

DVSEC Capability定义了必须以PCI Express Extended Capability Header、Designated Vendor-Specific Header 1、Designated Vendor-Specific Header 2开始,之后的才是厂商专用寄存器。

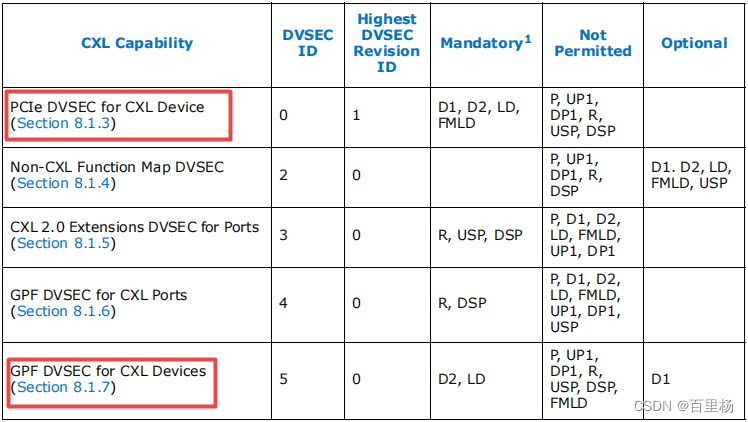

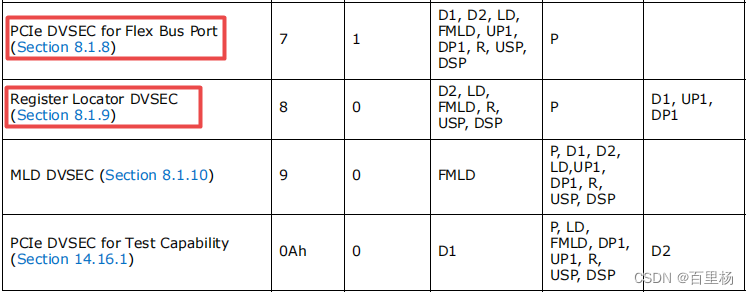

CXL 2.0协议中,定义的DVSEC Capabilities,如下所示:

CXL 2.0 Device必须实现的DVSEC Capability有:

- PCIe DVSEC for CXL Device

- GPF DVSEC for CXL Devices

- PCIe DVSEC for Flex Bus Port

- Register Locator DVSEC

2.1 Virtual Channel Extended Capability

Virtual Channel Extended Capability,如下所示:

但是以上这些寄存器, 仅有红框标注的寄存器才是每个设备必须具备的。

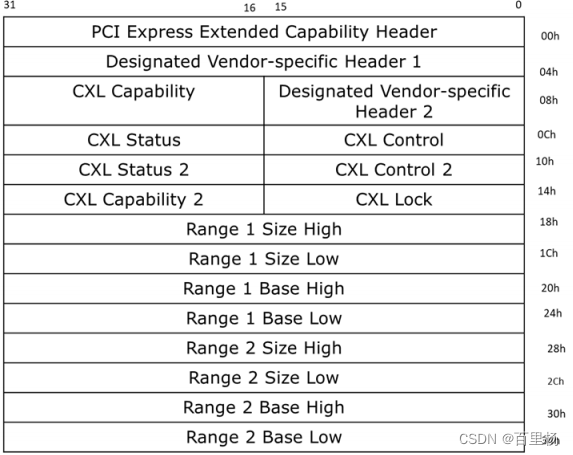

2.2 PCIe DVSEC for CXL Device

PCIe DVSEC for CXL Device,如下所示:

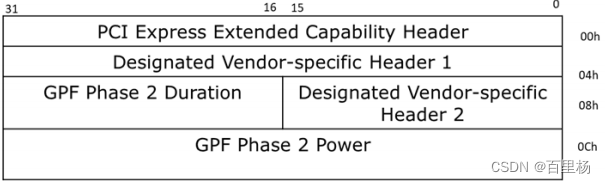

2.3 GPF DVSEC for CXL Devices

GPF DVSEC for CXL Devices,如下所示:

2.4 PCIe DVSEC for Flex Bus Port

PCIe DVSEC for Flex Bus Port,如下所示:

2.5 Register Locator DVSEC

Register Locator DVSEC,如下所示: