目录

1.环回模块——协调发送接收模块

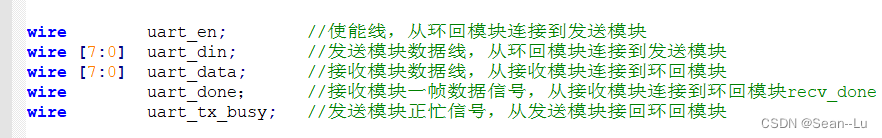

0.综上,信号线如下:

1.捕捉发送模块传过来recv_done信号的上升沿——得到recv_done_flag

2.recv_done_flag拉高,接收了一帧数据,紧接着可以给发送模块发送指令send_en、send_data

编辑2.顶层模块

0.信号线

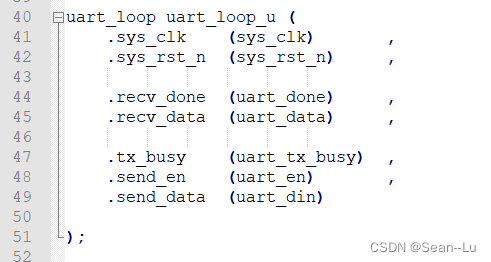

1.例化 接收+发送+回环模块

3.综合+约束、生成比特流+安装串口助手

1.打开Vivado,根据错误提示修正代码,综合一下看有没有其他错误——修正。

2.引脚约束——.xdc文件,生成bit流

2.1琢磨一圈后发现的问题——串口是PS的外设,而现在做的PL,即FPGA上的实验,需要额外的扩展模块如RS232等,才能实现串口通信!

3.安装串口调试助手 + 驱动+生成bit流,烧录+使用串口调试助手验证

4.因为没有扩展模块,本次实验就到此结束

1.环回模块——协调发送接收模块

什么时候再接收?什么时候再发送?——需要环回模块协调!

接收模块信号:uart_done——抓取上升沿,代表已经接收一帧完整的数据,发送一个send_en给发送模块——uart_en,告诉发送模块可以发送数据了!

发送模块信号:uart_tx_busy——高电平处于忙状态,此时环回不对发送模块不做任何操作。

//同样,需要定义临时寄存接收模块传过来的信号

0.综上,信号线如下:

同步时钟+复位,接收模块传两个输出信号:uart_done对应recv_done、uart_data存入临时寄存器recv_data。发送模块传两个输入信号:uart_en信号由send_en产生、uart_din由输出send_data产生!

1.捕捉发送模块传过来recv_done信号的上升沿——得到recv_done_flag

有了上升沿,就认为接受到了一帧有效的数据!——recv_done_flag拉高,紧接着可以给发送模块发送指令。

2.recv_done_flag拉高,接收了一帧数据,紧接着可以给发送模块发送指令send_en、send_data

//引入一个状态标志位——作用:准备启动发送过程

//此时,接收数据recv_data已经挂到了发送数据线send_data上

//tx_ready拉高,说明环回模块已经完全准备好,而且给发送模块的数据挂上了

//此时只需要将使能send_en打开,就能立刻将数据发送出去

//检测串口发送模块tx_busy是否空闲,必须要发送模块空闲,环回模块才能发送数据

//否则,发送模块正在发送一帧数据,结果立马接收了新的这一帧数据

//导致最后真正发送的数据是:前一帧的前几位+现在新的这帧数据的后几位——错误!

2.顶层模块

0.信号线

时钟+复位,然后就输出数据线rxd 和 输入数据线txd

1.例化 接收+发送+回环模块

接收

发送

回环

3.综合+约束、生成比特流+安装串口助手

1.打开Vivado,根据错误提示修正代码,综合一下看有没有其他错误——修正。

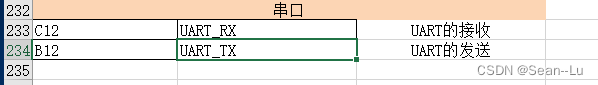

2.引脚约束——.xdc文件,生成bit流

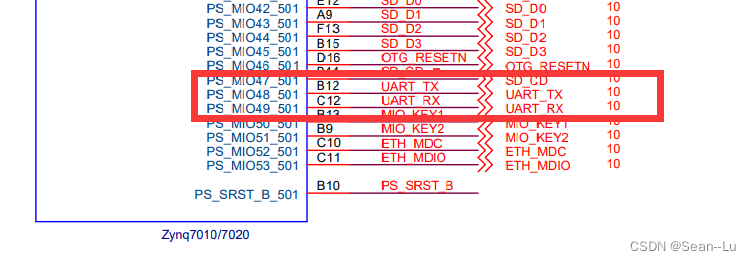

2.1琢磨一圈后发现的问题——串口是PS的外设,而现在做的PL,即FPGA上的实验,需要额外的扩展模块如RS232等,才能实现串口通信!

我的板子——zynq7020

PS端根本不存在端口——C12和B12

3.安装串口调试助手 + 驱动+生成bit流,烧录+使用串口调试助手验证

4.因为没有扩展模块,本次实验就到此结束

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)