实验四 译码器及其应用

一、实验目的

1.掌握中规模集成译码器的逻辑功能和使用方法

2.熟悉数码管的使用

二、实验原理

译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器可分为通用译码器和显示译码器两类。前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。若有n个输入变量,则有2n个不同的组合状态,就有2n 个输出端供其使用。而每一个输出所代表的函数对应于n个输入变量的最小项。

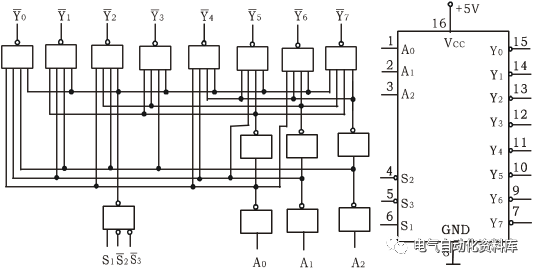

以3线-8线译码器74LS138为例进行分析,图4-1(a)、(b)分别为其

逻辑图及引脚排列。其中 A2 、A1 、A0为地址输入端, ~

~ 为译码输出端,S1、

为译码输出端,S1、 、

、 为使能端。

为使能端。

(a) (b)

图4-1 3-8线译码器74LS138逻辑图及引脚排列

表4-1为74LS138功能表

当S1=1, +

+ =0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S1=0,

=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S1=0, +

+ =X时,或 S1=X,

=X时,或 S1=X, +

+ =1时,译码器被禁止,所有输出同时为1。

=1时,译码器被禁止,所有输出同时为1。

表4-1

输 入 | 输 出 |

S1 |  + +

| A2 | A1 | A0 |

|

|

|

|

|

|

|

|

1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

0 | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

× | 1 | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

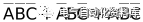

二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图4-2所示。若在S1输入端输入数据信息, =

= =0,地址码所对应的输出是S1数据信息的反码;若从

=0,地址码所对应的输出是S1数据信息的反码;若从 端输入数据信息,令S1=1、

端输入数据信息,令S1=1、 =0,地址码所对应的输出就是

=0,地址码所对应的输出就是 端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

根据输入地址的不同组合译出唯一地址,故可用作地址译码器。接成多路分配器,可将一个信号源的数据信息传输到不同的地点。

二进制译码器还能方便地实现逻辑函数,如图4-3所示,实现的逻辑函数是

Z= +ABC

+ABC

图4-2 作数据分配器 图4-3 实现逻辑函数

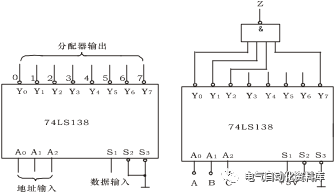

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如图4-4所示。

图4-4 用两片74LS138组合成4/16译码器

2.数码显示译码器

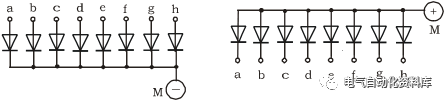

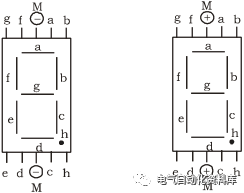

a.七段发光二极管(LED)数码管

LED数码管是目前最常用的数字显示器,图4-5(a)、(b)为共阴管和共阳管的电路,(c)为两种不同出线形式的引出脚功能图。

一个LED数码管可用来显示一位0~9十进制数和一个小数点。小型数码管(0.5寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色)的颜色不同略有差别,通常约为2~2.5V,每个发光二极管的点亮电流在5~10mA。LED数码管要显示BCD码所表示的十进制数字就需要有一个专门的译码器,该译码器不但要完成译码功能,还要有相当的驱动能力。

(a) 共阴连接(“1”电平驱动) (b) 共阳连接(“0”电平驱动)

(c) 符号及引脚功能

图 4-5 LED数码管

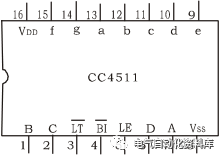

b.BCD码七段译码驱动器

此类译码器型号有74LS47(共阳),74LS48(共阴),CC4511(共阴)等,本实验系采用CC4511 BCD码锁存/七段译码/驱动器。驱动共阴极LED数码管。

图4-6为CC4511引脚排列

图4-6 CC4511引脚排列

其中

A、B、C、D — BCD码输入端

a、b、c、d、e、f、g — 译码输出端,输出“1”有效,用来驱动共阴极LED数码管。

— 测试输入端,

— 测试输入端, =“0”时,译码输出全为“1”

=“0”时,译码输出全为“1”

— 消隐输入端,

— 消隐输入端, =“0”时,译码输出全为“0”

=“0”时,译码输出全为“0”

LE — 锁定端,LE=“1”时译码器处于锁定(保持)状态,译码输出保持在LE=0时的数值,LE=0为正常译码。

表4-2为CC4511功能表。CC4511内接有上拉电阻,故只需在输出端与数码管笔段之间串入限流电阻即可工作。译码器还有拒伪码功能,当输入码超过1001时,输出全为“0”,数码管熄灭。

表4-2

输 入 | 输 出 |

LE |

|

| D | C | B | A | a | b | c | d | e | f | g | 显示字形 |

× | × | 0 | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|

× | 0 | 1 | × | × | × | × | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

|

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

|

0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

|

0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

|

0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

|

0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

|

0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

|

0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|

0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|

0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

|

0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 消隐 |

1 | 1 | 1 | × | × | × | × | 锁 存 | 锁存 |

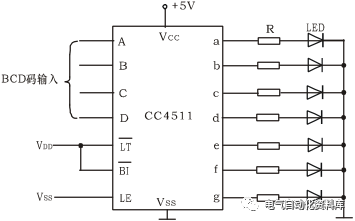

在本数字电路实验装置上已完成了译码器CC4511和数码管BS202之间的连接。实验时,只要接通+5V电源和将十进制数的BCD码接至译码器的相应输入端A、B、C、D即可显示0~9的数字。四位数码管可接受四组BCD码输入。CC4511与LED数码管的连接如图4-7所示。

图4-7 CC4511驱动一位LED数码管

三、实验设备与器件

1.+5V直流电源 2.双踪示波器

3.连续脉冲源 4.逻辑电平开关

5.逻辑电平显示器 6.拨码开关组

7、译码显示器 8.74LS138×2 CC4511

四、实验内容

1.数据拨码开关的使用。

将实验装置上的四组拨码开关的输出Ai、Bi、Ci、Di分别接至4组显示译码/驱动器CC4511的对应输入口,LE、 、

、 接至三个逻辑开关的输出插口,接上+5V显示器的电源,然后按功能表6-2输入的要求揿动四个数码的增减键(“+”与“-”键)和操作与LE、

接至三个逻辑开关的输出插口,接上+5V显示器的电源,然后按功能表6-2输入的要求揿动四个数码的增减键(“+”与“-”键)和操作与LE、 、

、 对应的三个逻辑开关,观测拨码盘上的四位数与LED数码管显示的对应数字是否一致,及译码显示是否正常。

对应的三个逻辑开关,观测拨码盘上的四位数与LED数码管显示的对应数字是否一致,及译码显示是否正常。

2.74LS138译码器逻辑功能测试

将译码器使能端S1、 、

、 及地址端A2、A1、A0分别接至逻辑电平开关输出口,八个输出端

及地址端A2、A1、A0分别接至逻辑电平开关输出口,八个输出端 依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表4-1逐项测试74LS138的逻辑功能。

依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表4-1逐项测试74LS138的逻辑功能。

3. 3/8线译码器组合成一个4线—16线译码器,并进行实验。

五、实验预习要求

1.复习有关译码器和分配器的原理。

2.根据实验任务,画出所需的实验线路及记录表格。

六、实验报告

1.画出实验线路,把观察到的波形画在坐标纸上,并标上对应的地址码。

2.对实验结果进行分析、讨论。

实验五 数据选择器及其应用

一、实验目的

1.掌握中规模集成数据选择器的逻辑功能及使用方法

2.学习用数据选择器构成组合逻辑电路的方法

二、实验原理

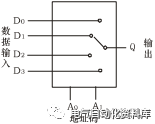

数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关,如图5-1所示,图中有四路数据D0~D3,通过选择控制信号 A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q。

数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。

数据选择器的电路结构一般由与或门阵列组成,也有用传输门开关和门电路混合而成的。

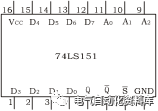

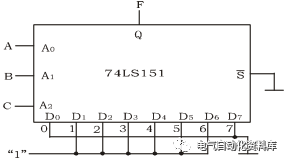

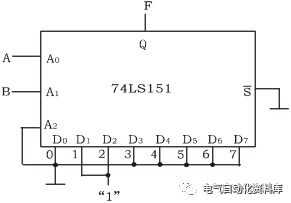

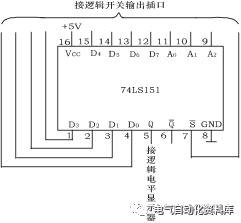

1.八选一数据选择器74LS151

74LS151为互补输出的8选1数据选择器,引脚排列如图5-2,功能如表5-1。

选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Q, 为使能端,低电平有效。

为使能端,低电平有效。

图5-1 4选1数据选择器示意图 图 5- 2 74LS151引脚排列

表5-1

输 入 | 输 出 |

| A2 | A1 | A0 | Q |

|

1 | × | × | × | 0 | 1 |

0 | 0 | 0 | 0 | D0 |

|

0 | 0 | 0 | 1 | D1 |

|

0 | 0 | 1 | 0 | D2 |

|

0 | 0 | 1 | 1 | D3 |

|

0 | 1 | 0 | 0 | D4 |

|

0 | 1 | 0 | 1 | D5 |

|

0 | 1 | 1 | 0 | D6 |

|

0 | 1 | 1 | 1 | D7 |

|

1)使能端 =1时,不论A2~A0状态如何,均无输出(Q=0,

=1时,不论A2~A0状态如何,均无输出(Q=0, =1),多路开关被禁止。

=1),多路开关被禁止。

2)使能端 =0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7中某一个通道的数据输送到输出端Q。

=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7中某一个通道的数据输送到输出端Q。

如:A2A1A0=000,则选择D0数据到输出端,即Q=D0。

如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推。

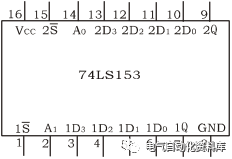

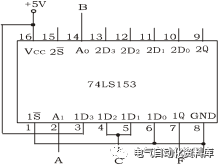

2.双四选一数据选择器 74LS153

所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。引脚排列如图5-3,功能如表5-2。

表5-2

表5-2

输 入 | 输 出 |

| A1 | A0 | Q |

1 | × | × | 0 |

0 | 0 | 0 | D0 |

0 | 0 | 1 | D1 |

0 | 1 | 0 | D2 |

0 | 1 | 1 | D3 |

图5-3 74LS153引脚功能

、

、 为两个独立的使能端;A1、A0为公用的地址输入端;1D0~1D3和2D0~2D3分别为两个4选1数据选择器的数据输入端;Q1、Q2为两个输出端。

为两个独立的使能端;A1、A0为公用的地址输入端;1D0~1D3和2D0~2D3分别为两个4选1数据选择器的数据输入端;Q1、Q2为两个输出端。

1)当使能端 (

( )=1时,多路开关被禁止,无输出,Q=0。

)=1时,多路开关被禁止,无输出,Q=0。

2)当使能端 (

( )=0时,多路开关正常工作,根据地址码A1、A0的状态,将相应的数据D0~D3送到输出端Q。

)=0时,多路开关正常工作,根据地址码A1、A0的状态,将相应的数据D0~D3送到输出端Q。

如:A1A0=00 则选择DO数据到输出端,即Q=D0。

A1A0=01 则选择D1数据到输出端,即Q=D1,其余类推。

数据选择器的用途很多,例如多通道传输,数码比较,并行码变串行码,以及实现逻辑函数等。

3.数据选择器的应用—实现逻辑函数

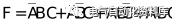

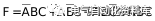

例1:用8选1数据选择器74LS151实现函数

采用8选1数据选择器74LS151可实现任意三输入变量的组合逻辑函数。

作出函数F的功能表,如表5-3所示,将函数F功能表与8选1数据选择器的功能表相比较,可知(1)将输入变量C、B、A作为8选1数据选择器的地址码A2、A1、A0。(2)使8选1数据选择器的各数据输入D0~D7分别与函数F的输出值一一相对应。

表5-3

输 入 | 输 出 |

C | B | A | F |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 |

0 | 1 | 0 | 1 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 1 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 1 |

1 | 1 | 1 | 0 |

即:A2A1A0=CBA,

D0=D7=0

D1=D2=D3=D4=D5=D6=1

则8选1数据选择器的输出Q便实现了函数

接线图如图5-4所示。

图5-4 用8选1数据选择器实现

显然,采用具有n个地址端的数据选择实现n变量的逻辑函数时, 应将函数的输入变量加到数据选择器的地址端(A),选择器的数据输入端(D)按次序以函数F输出值来赋值。

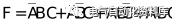

例2:用8选1数据选择器74LS151实现函数

(1)列出函数F的功能表如表5-4所示。

(2)将A、B加到地址端A1、A0,而A2接地,由表5-4可见,将D1、D2接“1”及D0、D3接地,其余数据输入端D4~D7都接地,则8选1数据选择器的输出Q,便实现了函数

接线图如图5-5所示。

表5-4

表5-4

图5-5 8选1数据选择器实现

的接线图

的接线图

显然,当函数输入变量数小于数据选择器的地址端(A)时,应将不用的地址端及不用的数据输入端(D)都接地。

例3:用4选1数据选择器74LS153实现函数

函数F的功能如表5-5所示 表5-6

输 入 | 输出 | 中 选 数据端 |

A | B | C | F | |

0 | 0 | 0 1 | 0 0 | D0=0 |

0 | 1 | 0 1 | 0 1 | D1=C |

1 | 0 | 0 1 | 0 1 | D2=C |

1 | 1 | 0 1 | 1 1 | D3=1 |

表5-5 输 入 | 输出 |

A | B | C | F |

0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 |

0 | 1 | 0 | 0 |

0 | 1 | 1 | 1 |

1 | 0 | 0 | 0 |

1 | 0 | 1 | 1 |

1 | 1 | 0 | 1 |

1 | 1 | 1 | 1 |

函数F有三个输入变量A、B、C,而数据选择器有两个地址端A1、A0少于函数输入变量个数,在设计时可任选A接A1,B接A0。将函数功能表改画成5-6形式,可见当将输入变量A、B、C中B接选择器的地址端A1、A0,由表5-6不难看出:

D0=0, D1=D2=C, D3=1

则4选1数据选择器的输出,便实现了函数 接线图如图5-6所示。

接线图如图5-6所示。

图5-6 用4选1数据选择器实现

当函数输入变量大于数据选择器地址端(A)时,可能随着选用函数输入变量作地址的方案不同,而使其设计结果不同,需对几种方案比较,以获得最佳方案。

三、实验设备与器件

1.+5V直流电源 2.逻辑电平开关

3.逻辑电平显示器 4.74LS151(或CC4512),74LS153(或CC4539)

四、实验内容

1.测试数据选择器74LS151的逻辑功能

接图5-7接线,地址端A2、A1、A0、数据端D0~D7、使能端 接逻辑开关,输出端Q接逻辑电平显示器,按74LS151功能表逐项进行测试,记录测试结果。

接逻辑开关,输出端Q接逻辑电平显示器,按74LS151功能表逐项进行测试,记录测试结果。

图5-7 74LS151逻辑功能测试

2.测试74LS153的逻辑功能

测试方法及步骤同上,记录之。

3.用8选1数据选择器74LS151设计三输入多数表决电路

1)写出设计过程

2)画出接线图

3)验证逻辑功能

4.用双4选1数据选择器74LS153实现全加器

1)写出设计过程

2)画出接线图

3)验证逻辑功能

五、预习内容

1.复习数据选择器的工作原理;

2.用数据选择器对实验内容中各函数式进行预设计;

六、实验报告

用数据选择器对实验内容进行设计、写出设计全过程、画出接线图、进行逻辑功能测试;总结实验收获、体会。