点击上方蓝字

给一个关注吧

数电复习之任意进制计数器设计

首先再提醒一下,四、五章的内容之前已经写过,需要的同学可以翻一下本公众号历史消息,最开始的几篇就是。本篇内容是将之前落下的用集成计数器芯片进行任意进制计数器设计(用N进制实现M进制)这一部分补上,因为是第五章的考试重点。

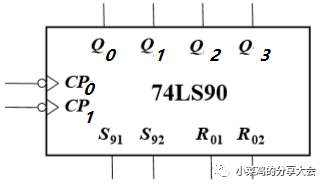

纠正一下之前的一篇文章的一个图片的疏漏,文章标题是“时序逻辑电路设计(二):异步计数器设计及集成计数器芯片的功能”,最后的74LS90的图片上的标注和下面的介绍文字有出入,在这篇文章中更正一下,当然这个芯片不在考察范围内。如下图:

01

M

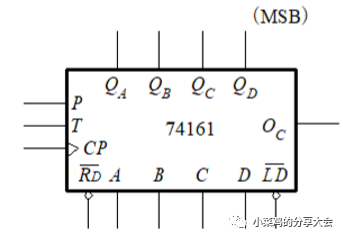

此时应当使用单片,对于74160和74161来说,他们都有异步复位端和置数端,因此都有置零法和置数法两种方法。这里再将74161芯片放上来以便学习(两款芯片端口一摸一样,区别请翻看之前的文章):

1.置零法

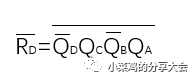

置零法的原理在于在暂稳态清零这个操作。什么叫暂稳态呢?我们以实现五进制加法计数器举个栗子:五进制中,0000-0100为五个稳态,最后的”5“,也就是0101是不应该出现的,但是我们希望在出现0101的时候立即回到0000,因此0101会暂时的出现作为清零信号接入异步复位端—RD非,因此0101是暂稳态。这里的重点在于,置零法我们是要将暂稳态的信号接入复位端,五进制就是 ,需要大家提起注意。还有一点是,当改动进制之后,原有的进位端不再可用,需要自己搭建。

,需要大家提起注意。还有一点是,当改动进制之后,原有的进位端不再可用,需要自己搭建。

另外对于置零法,很大的一个缺点在于暂稳态的问题,由于维持时间短,可能无法有效复位,解决方法是将原有的置零信号与一个CP信号接入一个基本RS触发器,CP接R非,输出Q非接入异步复位端,可以使得清零信号长时间保持。

2.置数法

上图中的ABCD就是预置数,同样以上面的五进制为例,这时我们只需要将0100接与非门输入到LD非,在下一个CP到来之时,输出就跳转到预置的数,依次对应。当然这里允许不跳转回0000,可以跳转到任意数值,最后的进制通过状态数来确定。

02

M>N

1.M=N1*N2

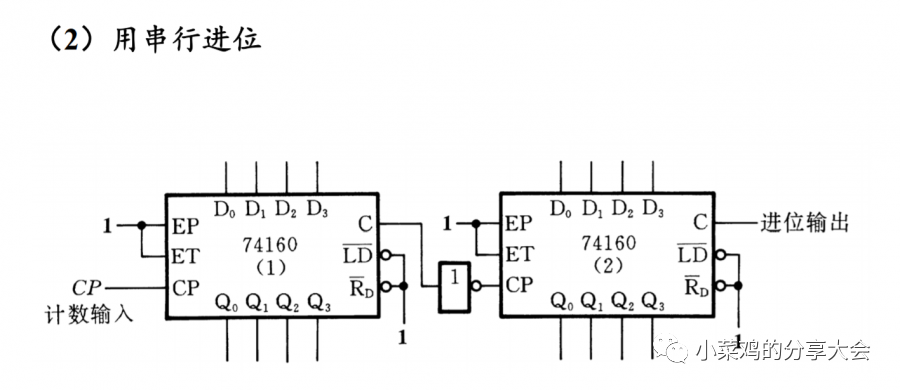

这里可以用串行进位或并行进位实现,如图用74160实现100进制:

这里需要特别注意的一点是,这两片的输出绝不能一起读!!!他们的输出分别代表十位数字和个位数字,并不是同一个二进制数。至于串并行具体的原理比较简单不再解释,希望读者自行体会。

2.M是素数

这种情况可以先寻找一个比M大并且容易拆分的合数K,用串并行的方法表示出K,于是情况成为了K>M,即第一种情况,采用置零法或置数法。

至于最终计数器的自启动问题,由于采用的是集成计数器芯片,个人认为是并不需要考虑自启动问题的,我记得上课的时候应该是提到过,如果有读者有不同的想法欢迎私信讨论。

数电的重点到此基本结束,后面的内容就不算是特别重要的了,复习时应当注意侧重点的把握,因此不再更新,文中如若有何疏漏,烦请读者不吝赐教!!!感谢各位读者的阅读、转发与关注!!!