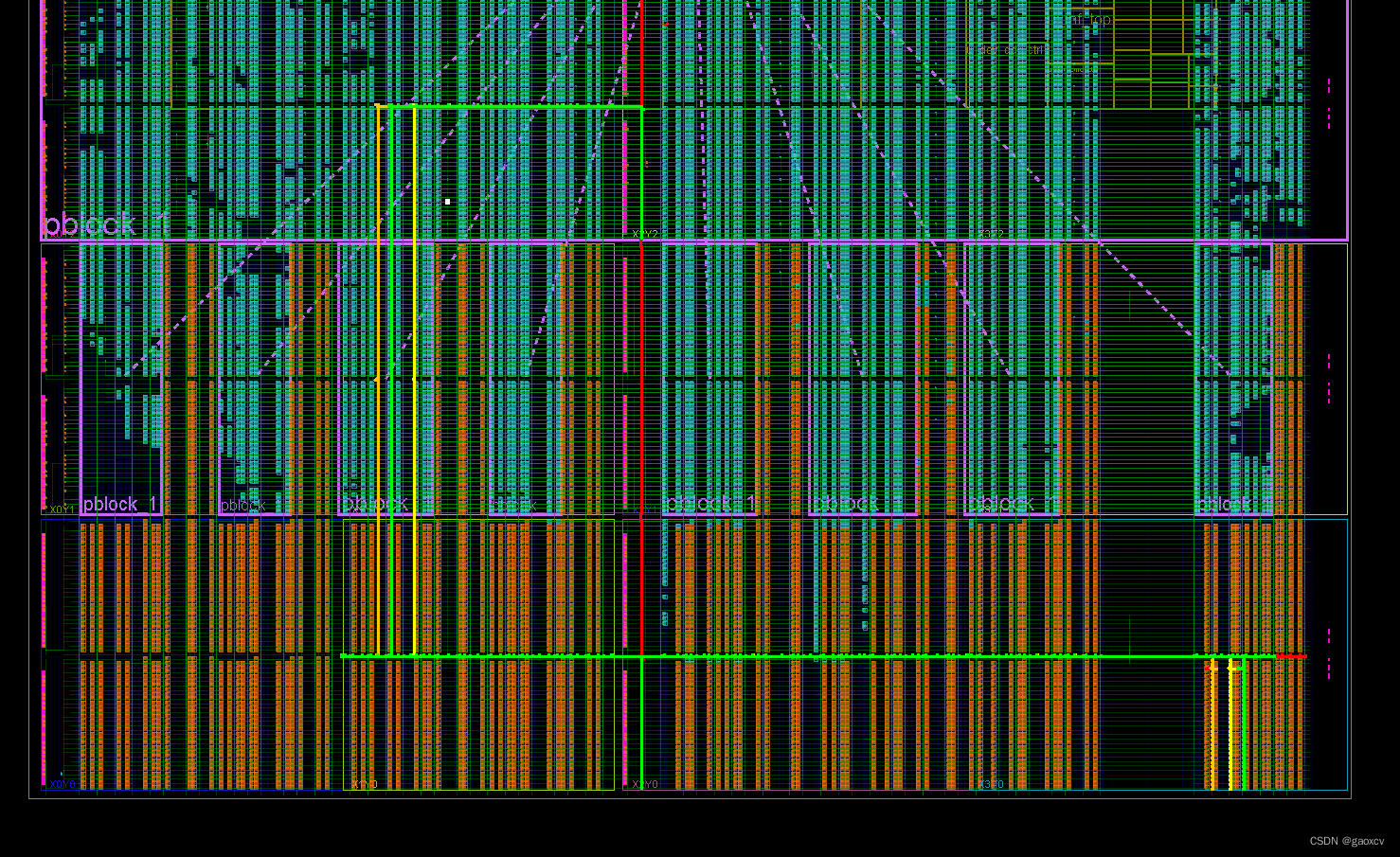

ku040 的 skew ,同一个 clk 下的不同寄存器, clk 到达时间可能会差 300ps,跟 clk 走线的长度相关,一般同一个 bank内 clk 在 30ps 之内

但是不同的 clk,即使从同一个 mmcm/pll 的不同管脚发出,因为走线差异比较大,到达相同位置的寄存器,可能有 800 ps 的 skew

红色 2.211

橙色 3.039

黄色 2.968

绿色 2.975

可以看到,因为红色走线没有绕圈,到最右边的寄存器比其他 clk 少 800ps

解决:

在 clock_wizard 中勾选 matched_routing 选项

走线变为了以下的方式

红色 2.648

橙色 2.669

黄色 2.699

绿色 2.691

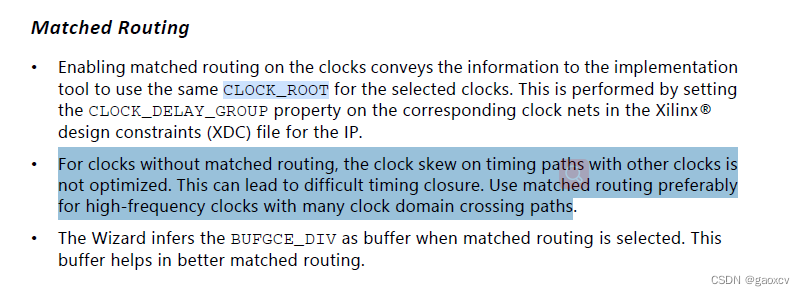

ug065 p29 有如下解释

xdc 的 property 说明在 ug912

加入此选项后 place 变得困难,有可能会失败,需要多尝试几次

jitter 在 clock_wizard 的summary 界面,在时序分析界面也可以看到最终 jitter 的合成公式