MIPI接口在移动设备中被广泛应用,主要用于传输图像传感器、液晶显示器等外设的数据。以MIPI DPHY v1.2为例,它包含一个CLK lane和若干个DATA lane(可配置),每个lane的最高速率可达到2.5Gbps。对比SerDes接口,MIPI DPHY虽然pin数量和传输速率都处于劣势,但是其静态功耗(无数据传输时)非常低,latency也短,所以仍然具有不可替代的优势。

一个典型的MIPI系统如下图示:

MIPI RX一般接image sensors(比如手机摄像头),而MIPI TX接显示器或系统主控(比如手机AP)。 如果按sensor和display来分,MIPI传输协议有CSI2和DSI两种。两者在物理层并无不同,但是上层协议差别很大。对“寸土寸金”的移动设备芯片来说,最好能有一种兼容设计,CSI2和DSI复用物理层逻辑,只是在上层做协议区分。

相对于MIPI RX来说,MIPI TX需要COMBO controller的场景更多,所以这里以MIPI TX举例,如下图示:

下面解释一下每个模块的功能:

| Block |

Function Description |

| Pixel Assembly |

把AXI Stream上的pixel转换成符合MIPI协议的Byte对齐格式 |

| PACK |

打包器,按照CSI2/DSI协议将Byte组装成MIPI packets,并且插入必要的同步包,比如SOF, EOF, 等等 |

| TPG |

测试图案生成器,用于系统测试和debug |

| Lane Management |

主要功能有两个,一是对多路数据流进行仲裁(MIPI支持最多4个Virtual Channel),二是将数据分配到一个或多个data lane上 |

| DPHY Interface Controller |

驱动PPI接口,管理link status等 |

| REG BANK |

寄存器控制单元 |

| TSG |

Timing Sync Generator,主要用于产生DSI所需要的sync events |

| RST |

复位管理单元 |

| INT |

中断管理单元 |

| DPHY CFG |

DPHY的控制单元 |

Pixel Assembly:以RAW10举例,内存中一般按照像素对齐来进行存储,但是MIPI RAW10格式要求高8-bit字节对齐,低2-bit则每隔4个像素就组成1字节。如下图示:

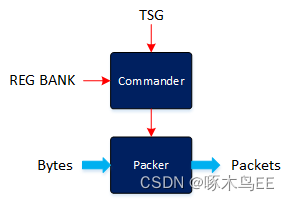

PACK:这个模块是实现CSI2/DSI协议分离的关键模块。CSI2/DSI除了物理层完全相同,在传输层也有很多相似性,比如它们都遵循同样的header和footer规则,不同的只是header内容。于是PACK模块被设计成由两部分组成:Commander和Packer。Commander处理CSI2/DSI的协议内容,并按照固定的规则翻译成指令控制Packer组装MIPI packets。

比如对于CSI2协议,Commander由数据流驱动,在收到第一包数据时发命令给Packer,要求它立即组装一个SOF包,然后再发组装数据包的命令;在发完一帧图像的最后一包数据后,Commander又会发组装EOF包的命令。

DSI协议会相对复杂一些,以video mode为例,Commander由TSG驱动,按照严格的时序命令Packer进行打包。不过Packer对此毫无感知,它只是兢兢业业地完成Commander下达的指令。由于DSI的实时性要求,系统可能发生断流或溢出的错误,这些也是DSI比CSI2复杂的地方。

实际的设计比上面的举例要复杂得多,比如CSI2还要处理embedded data,而DSI需要支持任意时刻的SP插入(主要用于控制显示器的关闭、复位、工作模式等)。不过最重要的还是Commander+Packer的设计思想,有了这个主体,复杂的功能都可以比较容易地在这个框架内实现。

Lane Management: 最多会有四路数据流参与仲裁,默认使用Round-Robin算法进行权限分配,也可以配置成固定优先级。权限分配的颗粒度以packet为单位,一个packet之内的数据传输是不会被打断的。Lane distributor会把packet拆分成byte cells,然后根据data lane数量的配置进行分配。为了保证传输效率,一个packet在MIPI lanes上的传输应该是连续的,所以这里需要data buffer来缓存至少一个packet的数据,并通过handshake buffer与PPI driver逻辑进行通信。

DPHY Interface Controller:前面介绍了,其主要功能就是PPI driver。PPI是MIPI DPHY与MIPI Controller间的标准接口协议,可以支持HS, LPDT, ULPS, Turn-Around等多种传输模式或状态。其信号比较多,时序也很多,这里就不一一展开了。

最后来说说仿真:为了简化验证设计,我们可以忽略Controller与DPHY间的信号,直接拿DPHY输出与Monitor进行比较。下图是一种UVM验证环境的示例。