前言

本文首发于微信公众号<FPGA学习者>

`嗨,你来了,来了就带点东西走吧,比如:带走下面的知识~

21.FPGA组成三要素

①可编程逻辑功能块,CLB;

②片内互联线,(Programmable Interconnect);

③可编程输入输出块(I/O);

1️⃣CLB

CLB是FPGA内的基本逻辑单元(LE,Logic Element)。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包括:查找表、D触发器、进位链……

只用LUT,实现的是组合逻辑;

只用D触发器,实现的是单纯的信号打拍;

D触发器和LUT都使用,实现时序逻辑。

=<

在Xilinx公司的FPGA器件中,CLB由多个(一般为4个或2个)相同的Slice和附加逻辑构成。每个CLB模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM和分布式ROM。

Slice是Xilinx公司定义的基本逻辑单位,一个Slice由两个 4输入的函数、进位逻辑、算术逻辑、存储逻辑和函数复用器组成。算术逻辑包括一个异或门(XORG)和一个专用与门(MULTAND),一个异或门可以使一个Slice实现2bit全加操作,专用与门用于提高乘法器的效率;进位逻辑由专用进位信号和函数复用器(MUXC)组成,用于实现快速的算术加减法操作;4输入函数发生器用于实现4输入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的两个输入函数为6输入,可以实现6输入LUT或64比特移位寄存器);进位逻辑包括两条快速进位链,用于提高CLB模块的处理速度。

=<

2️⃣可编程内部互联资源

包括各种长度的连线线段和一些可编程连接开关;(Altera内部采用行、列局部快速通道)。

3️⃣可编程输入输出块

包括输出寄存器、输入寄存器、输出使能寄存器、输入延迟链、输出延迟链、上拉电阻等。

22.查找表(LUT)

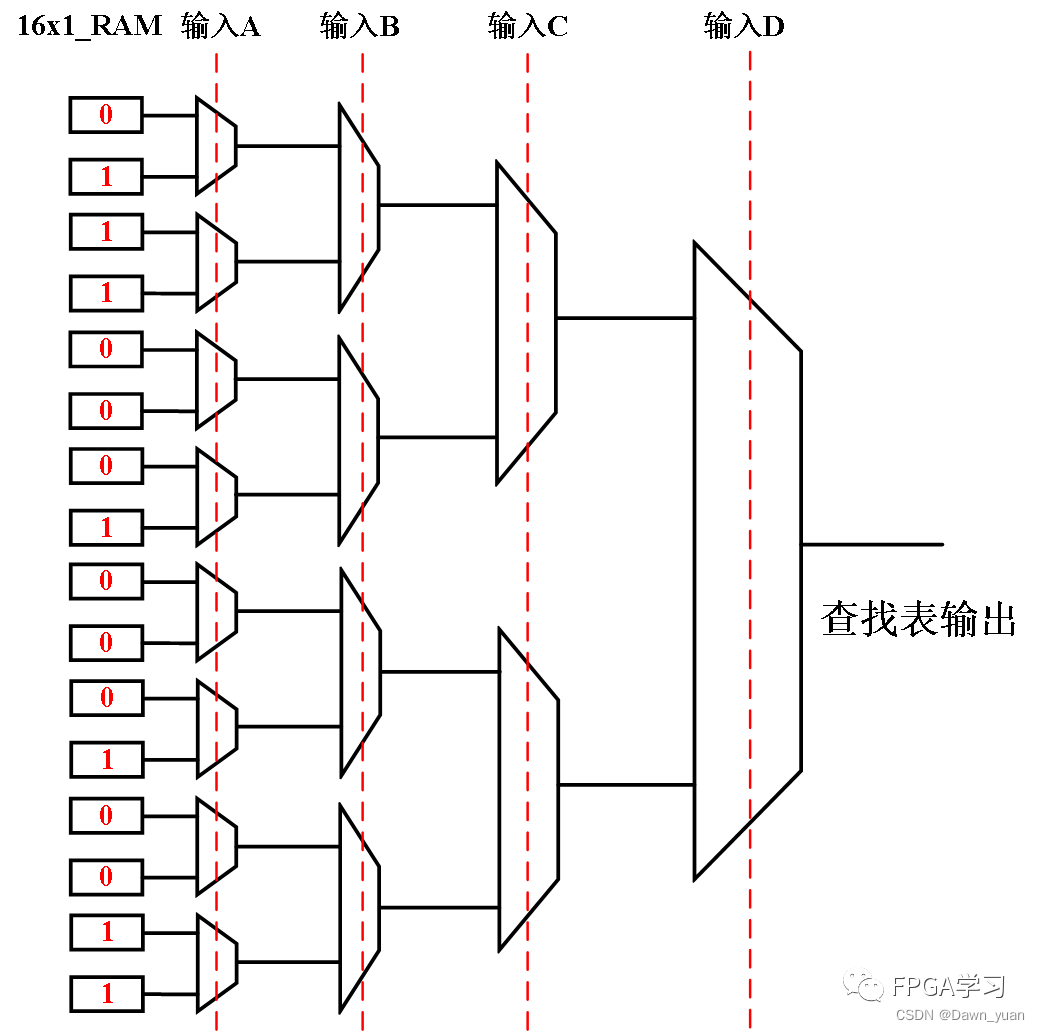

查找表(look-up-table)简称LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。 如下图所示:

假设当输入A、B、C、D为0时选择上方通道,输入为1时选择下方通道;

FPGA的可编程原理就是要改变16x1_RAM中的初始值。

一个N输入的查找表LUT,可以实现N个输入变量的任何逻辑功能,如N输入“与”,N输入的“异或”等等。

输入多于N个的函数,方程必须分开用几个查找表来实现。

23.锁存器(latch)/触发器

latch是电平触发,register是边沿触发,register在同一时钟边沿触发下动作,符合同步电路的设计思想,而latch则属于异步电路设计,往往会导致时序分析困难,不适当的应用latch则会大量浪费芯片资源。

为什么锁存器不好?

1)锁存器对毛刺不敏感,很容易在信号上产生毛刺;

2)而且也没有时钟信号,不容易进行静态时序分析。

正是因为这两个原因,我们在FPGA设计时,尽量不用锁存器。

注意:

<FPGA中只有LUT和DFF的资源,没有现成的Latch,所以如果要用Latch,需要更多的资源来搭出来。>

这个观点不完全正确。

在Xilinx的FPGA中,6系列之前的器件中都有Latch;6系列和7系列的FPGA 中,一个Slice中有50%的storage element可以被配置为Latch或者Flip-Flop,另外一半只能被配置为Flip-Flop。比如7系列FPGA中,一个Slice中有8个Flip-Flop,如果被配置成了Latch,该Slice的另外4个Flip-Flop就不能用了。这样确实造成了资源的浪费。但是在UltraScale的FPGA中,所有的storage element都可以被配置成Flip-Flop和Latch。

24.亚稳态

亚稳态,是因违反寄存器的建立时间和保持时间而产生的。

逻辑电路中绝大多数的时序问题基本都是因为这个原因产生的。

由于寄存器在任何信号通路中都有特定的建立时间和保持时间,这要求输入信号要保持稳定。但如果信号在这段时期发生了变化,那么输出将是未知的。这个未知的状态便称为亚稳态。

危害:

只要系统中存在异步元件,那么亚稳态就是无法完全避免的。产生亚稳态后,寄存器输出在稳定之前可能是毛刺、振荡、固定的一个电压值。其他与之相连的数字元件收到它的亚稳态,也会发生逻辑混乱,最糟糕的情况就是系统直接崩掉。

常见情况:

①输入信号是异步信号

②时钟偏移/摆动(上升/下降时间)高于容限值。(时钟信号质量不好)

③信号在两个不同频率或者相同频率但相位和偏移不同的时钟域下跨时钟域工作。

④组合延迟使寄存器的数据输入在亚稳态窗口内发生变化。

解决方法:

在实际的FPGA设计中,人们不会想着怎么降低发生亚稳态的概率,而是想着怎么减小亚稳态的影响。常见的方法有以下几种:

1)降低系统时钟频率

2)用反应更快的触发器

3)引入同步机制,防止亚稳态传播(可以采用前面说的加两级触发器)。异步信号同步化(两级触发器),采用FIFO对跨时钟域数据通信进行缓冲对复位电路采用异步复位、同步释放处理。

4)改善时钟质量,用边沿变化快速的时钟信号。

25.逻辑电平

常用逻辑电平:12V,5V,3.3V。

TTL和CMOS不可以直接互连,由于TTL是在0.3-3.6V之间,而CMOS则是有在12V的有在5V的。CMOS输出接到TTL是可以直接互连。TTL接到CMOS需要在输出端口加一上拉电阻接到5V或者12V。

用CMOS可直接驱动TTL;加上拉电阻后,TTL可驱动CMOS。

26. 逻辑最小项

在一个有n个变量的逻辑函数中,包括全部n个变量的乘积项(每个变量必须而且只能以原变量或反变量的形式出现一次)称为最小项。

n个变量有2n个最小项,比如当n=3时,此逻辑函数应有23=8个最小项。分别是:A’B’C’,A’B’C,A’BC’,A’BC,AB’C’,AB’C,ABC’,ABC.

最大项就是全部n个变量的加和了。

性质

1)对于任意一个最小项,输入变量只有一组取值使得它的值为1,而在变量取其他各组值的时候,这个最小项的值都为0。

2)不同的最小项,使得它的值为1的那一组输入变量取值也不同。

3)对于输入变量的任何一组取值,任意两个最小项的乘积为0。

4)对于输入变量的任何一组取值,全体最小项的和为1。

总结

以上就是今天要讲的内容,下期再见~

往期精彩

笔试|面试|FPGA知识点大全系列(1)

笔试|面试|FPGA知识点大全系列(2)

笔试|面试|FPGA知识点大全系列(3)

笔试|面试|FPGA知识点大全系列(4)