前言

题目:单相正弦逆变电源

具体软件部分请参照从零开始做单相逆变电源(软件)]

一、主要模块需求

本系统以TM4C123GH6PM单片机/FPGA为控制核心,基于正弦脉冲宽度调制(SPWM),设计制作了单相正弦波逆变电源。所用的电路模块包括全桥电路、辅助电源、互感器、采样电路、继电器、光耦器件

1、全桥模块

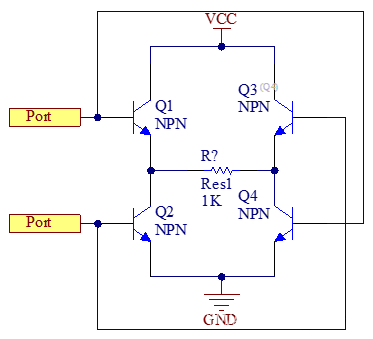

下图为全桥电路结构图。

全桥电路由两个相位对称的PWM波控制,全桥电路中互为对角的两个三极管(Q1、Q2和Q3、Q4)同时导通,而同一侧的上下两个三极管交替导通,从而实现将直流电压转换为交流电压。改变PWM的占空比,将改变电压有效值。相比于半桥电路,在输入电压相同的的情况下,全桥电路的输出电压有效值更高。

在本次实验中,用两个半桥模块级联形成全桥电路。

半桥模块、辅助电源模块、继电器参照从零开始开关电源

2、采样电路

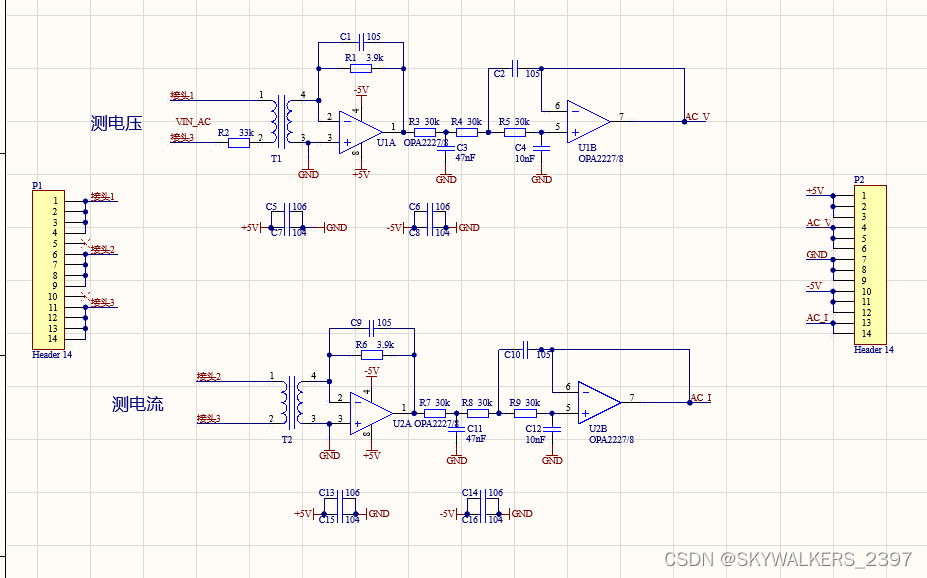

输出电压为10V交流电,选取ADS8688作为采样芯片,同时使用互感器对输出电压进行预处理使其能够被采样芯片读取。

原理图如下:

不同的互感效率不同,推荐使用2192

光耦

在FPGA的输入输出端口,都需要使用光耦进行隔离(不使用在正常情况下不会由影响,但如果出现问题就会导致FPGA出现故障,所以一般需要使用)

为了防止外来信号影响,各通道的输入输出都要下拉

部分电路PCB及原理图见压缩包