0. 前言

哈喽!“二舅”最近和你们一样,不断被鞭策,今天抽个小空给大家带来的是前几天做的一套笔试题,名称如标题所示,希望大家正确食用(点赞+转发+评论)

本次笔试题总体来说不难,一共11个题,没有选择填空,全是简答题。时间还是有一点点紧的。

这里不得不说这个系统,真的很难用,大家做题的时候注意一下,代码题需要自己手敲空格,真鸡肋呀!

下边是具体的题目,仅仅是回忆,哈哈哈!!!

注意:答案中可能涉及到很多知识点没有同步到微信公众号,之后会慢慢同步过来的,这里给出答案链接,大家可以先看看博客那边的答案,谢谢!

博客链接:

https://blog.csdn.net/qq_40549426/article/details/125948868

1. 题目 & 答案

第一题

有符号二进制转十进制(5)

解析:这些题也是基本必考的,大家多看看数电书。

第二题

十进制小数转二进制小数(5)

解析:这些题也是基本必考的,大家多看看数电书。

第三题

代数式化简的题(5)

解析:考察的是吸收律

第四题

skew和jitter对于setup和hold的影响(10)

解析:clock jitter始终是对性能造成负面的影响,一般设计中都需要专门留取10%左右的margin来保证。如何减小skew是后端布设clock tree的主要考量。再就是可以根据建立时间、保持时间的满足条件进行回答。

第五题

谈一下你对skew和jitter的理解(10)

解析:

jitter:由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,就是 jitter,指的是时钟周期的变化,也就是说时钟周期在不同的周期上可能加长或缩短。它是一个平均值为 0 的平均变量。指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者 PLL 内部电路有关,布线对其没有影响。由于跟晶振本身的工艺有关,所以在设计中无法避免它能带来的影响,通常只能在设计中留有一定的余量。

skew:是指同样的时钟产生的多个子时钟信号之间的延时差异。skew 通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了 skew。完成布局布线后,物理路径延时是固定的,所以在设计中考虑到时钟偏移,就可以避免偏移带来的影响。

第六题

跨时钟域的编程题(20)

解析:可以参考一下牛客上边的相关题目。

第七题

有个显示的需求,让你说一下想法(15)

解析:我觉得应该没有标准答案吧!发散性问题(怎么感觉这种题就是公司出现了技术上的难题,出来收割一波呢???猜的啊,毫无依据)

第八题

实现上边的想法(15)

解析:进一步证实了我的想法!!!哈哈哈

第九题

CRC(20)

解析:这个我之前写过一篇文章,大家可以去之前的文章中找找,讲的就是CRC。

第十题

SR锁存器的图形分析题(10)

解析:一步一步分析就行,让你画波形图。

第十一题

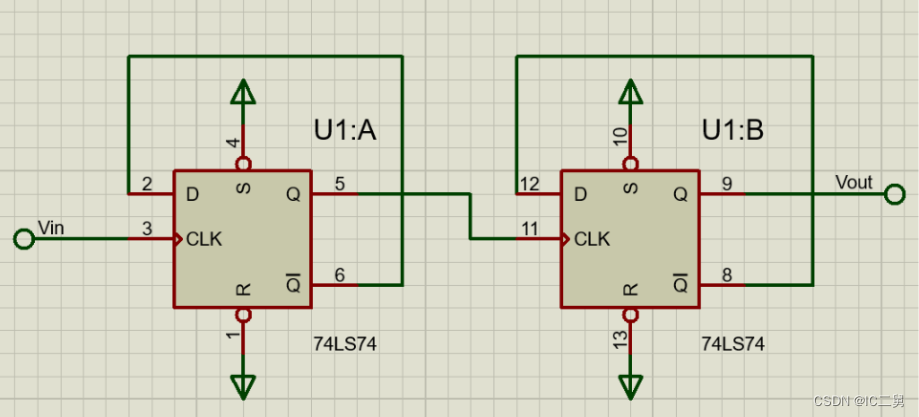

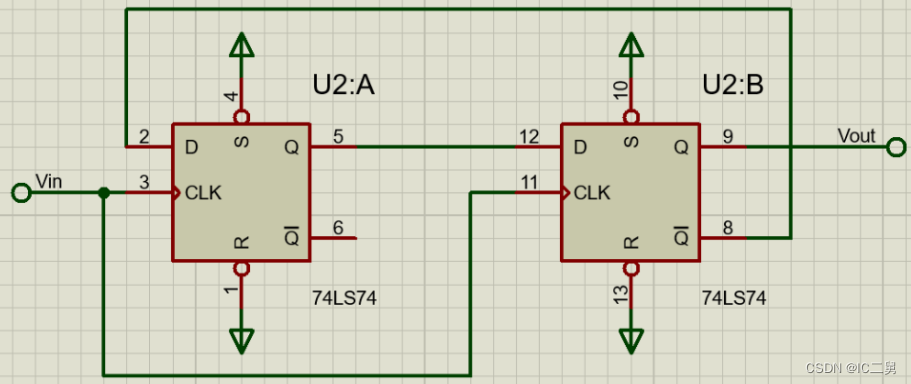

用寄存器、与或非门实现一个四分频电路(10)

解析:这个实现可以有两种方式,我记得好像是一道电子竞赛题目。

第一种就是先实现一次二分频,再连接一个二分频,这就实现了四分频。

第二种就是直接实现四分频。

声明

本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!!

本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!!

如果觉得对你有用的话,记得收藏+评论!!!

全网各平台同名===> “IC二舅”

下一期如果有大家想看的 或者 哪块不懂想学习的,可以私聊或在群里提问都可以,“二舅” 给你安排上!!!