原文链接:https://juejin.cn/post/7123461617299226660

约束命令

set_input_delay -clock CLK -max 2.0 [get_ports IN]

set_input_delay -clock CLK -min 2.0 [get_ports IN]

set_output_delay -clock CLK -max 2.0 [get_ports OUT]

set_output_delay -clock CLK -min 2.0 [get_ports OUT]

标题附加问题:input delay 和setup time之间大概的数量关系是?(以下来源网络)

- 如果是block的input和output delay,可以预先分配,比如输入端,输出端各1/3,中间的连接1/3。

- block的端口最好都flop-in,flop-out

- 如果是chip IO,要考虑其他芯片的IO时序和电路板上面的延迟,比较麻烦

- set_input_delay/set-output_delay是设置外面的delay,从而保留芯片内部的IO delay来约束input io到flop和flop到output io的delay。一般紧约束为外面留70%,里面留30%,但实际上有些port要调整,不是每个port都需要一样的值。

set_input_delay [expr 0.7*$clkperiod] -clock $clk [all_valid_inputs]

set_output_delay [expr 0.7*$clkperiod] -clock $clk [all_outputs]

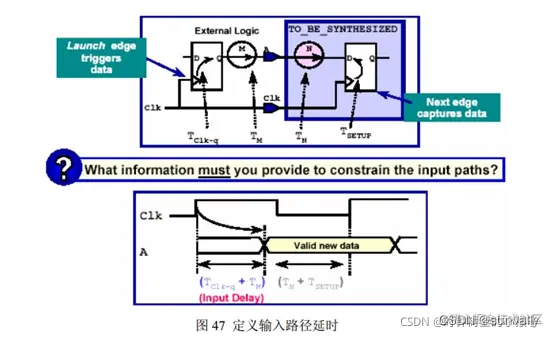

对input delay的理解

从上图可以看出, 我们所要定义的输入延时是指被综合模块外的寄存器触发的信号在到达被综合模块之前经过的延时, 在上图中就是外围触发器的clk-q的延时加上M电路的延时。当确定这段延时之后, 被综合模块内部的电路延时的范围也可以确定下来了。 假如时钟周期是 20ns,输入延时是 4ns,内部触发器的建立时间为 1.0ns,那么就可以推断出要使电路正常工作, N 电路的延时最大不能超过 20-4-1.0=15.0 ns。

set_input_delay -clock CLK -max 4 [get_ports A]

如上面的语句指出了被综合模块的端口 A 的最大输入延时为 4ns。 -max 选项是指明目前设置的是输入的最大延迟,为了满足时序单元建立时间的要求。

另外还有一个选项是-min, 它是针对保持时间的约束使用的。 -clock 是指出这个端口受哪个时钟周期的约束。

对于输入延时input delay,最大值应当是Tperiod-(TNmax+Tsetup),其中TN是上图中从input io到flop之间的组合逻辑电路N的延时,因为要满足建立时间的要求如下:

input delay+ TNmax+Tsetup < Tperiod

input delay < Tperiod - (TNmax+Tsetup)

最小值应该是Thold-TNmin,因为要满足保持时间的要求如下

input delay + TNmin > Thold

input delay > Thold - TNmin

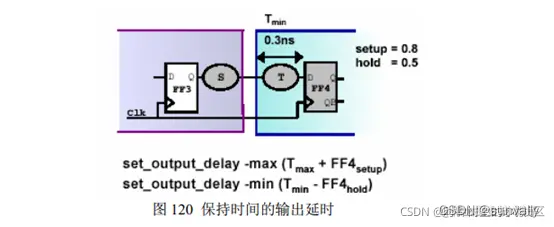

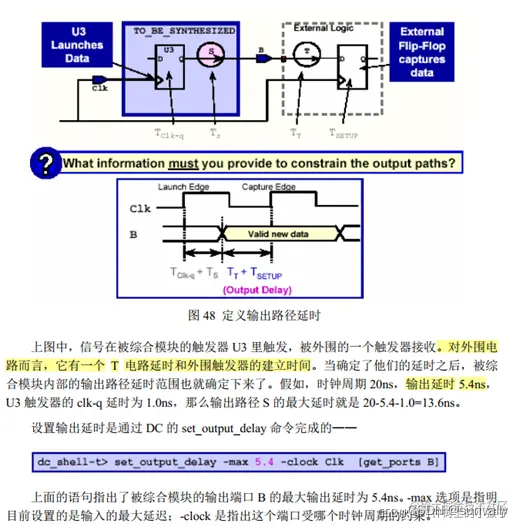

标题对output delay的理解

The delay_value represents the amount of time that the signal is required before a clock edge. For maximum output delay, this usually represents a combinational path delay to a register plus the library setup time of that register. For minimum output delay, this value is usually the shortest path delay to a register minus the library hold time.

对于输出延时output delay,规定的是被综合模块输出信号到达外围电路触发器D端所用的延时。

output delay最大值是组合逻辑电路(上图中T电路)延时最大值加上目标触发器的setup time,因为必须满足目标触发器的setup要求,在data required time之前到来,即

Tco + Ts + max output delay < Tperiod

Tco + Ts+ (TTmax+Tsetup) < Tperiod

所以有

max output delay = TTmax+Tsetup

output delay最小值是组合逻辑电路(上图中T电路)延时最小值减去目标触发器的hold time,相当于

Tco+Ts+TTmin>Thold

Tco+Ts+(TTmin-Thold)>0

所以有

min output delay = TTmin - Thold