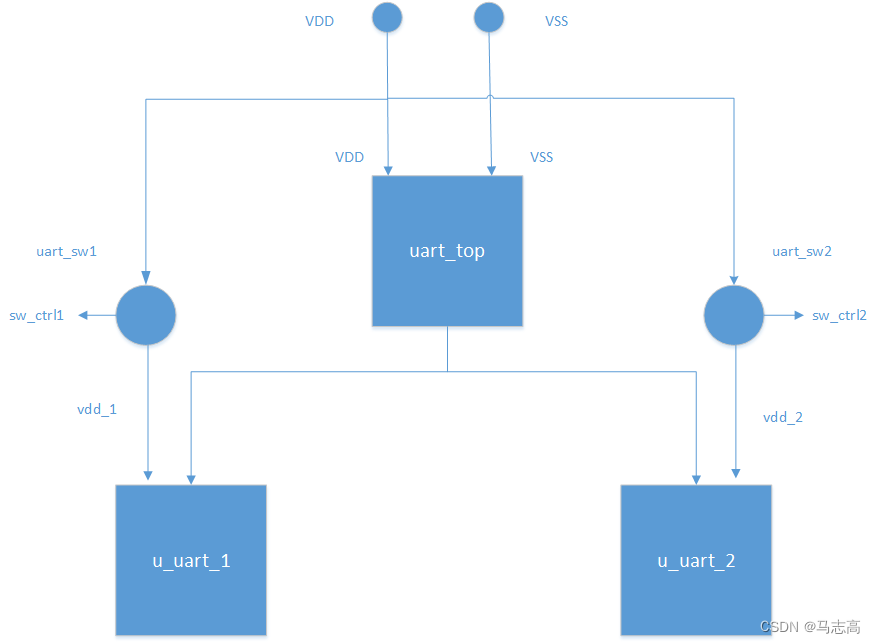

一.结构描述

这里是一个uart_top模块里面例化了两个uart,分别给两个模块给了power_switch,用于电源控制,对这两个模块分别进行隔离关断来写一个简单的upf。

二.代码分析

1.电压域

### create power domain ###

create_power_domain {uart_top}

create_power_domain {uart_1} -elements {u_uart_1}

create_power_domain {uart_2} -elements {u_uart_2}

注意点1:电压域的中这里没有用到scope的内容,create_power_domain {uart_top} 这表达的含义就是uart_top为顶层的意思,不需要使用scope。

注意点2:代码第二行中的{uart_1}是取的名字,是可以随意取的,不影响代码。

2.供电端口及网络

### power supply network ###

create_supply_port {VDD}

create_supply_net {VDD} -domain {uart_top}

connect_supply_net {VDD} -ports {VDD}

create_supply_port {VSS}

create_supply_net {VSS} -domain {uart_top}

connect_supply_net {VSS} -ports {VSS}

create_supply_net {VDD} -domain {uart_1} -reuse

create_supply_net {VSS} -domain {uart_1} -reuse

create_supply_net {VDD_1} -domain {uart_1}

create_supply_net {VDD} -domain {uart_2} -reuse

create_supply_net {VSS} -domain {uart_2} -resue

create_supply_net {VDD_2} -domain {uart_2}

### specfiy the primary supply ###

set_domain_supply_net {uart_top} -primary_power_net {VDD} -primary_ground_net {VSS}

set_domain_supply_net {uart_1} -primary_power_net {VDD_1} -primary_ground_net {VSS}

set_domain_supply_net {uart_2} -primary_power_net {VDD_2} -primary_ground_net {VSS}

注意点1:create_supply_port 为定义端口,create_supply_net为定义线,connect_supply_net…ports是线和端口连起来,这里VDD用了两次,一个是端口名字,一个是线的名字。

注意点2:VDD是可以复用的,复用的方法为-reuse。

注意点3:定义好端口,线,连上之后,需要使用set_domain_supply_net明确供电线和地线。

3.电源开关

### power switch ###

create_power_switch uart1_sw \

-domain {uart_1} \

-input_supply_port {vin VDD} \

-output_supply_port {vout VDD_1} \

-control_port {swctrl sw_ctrl1} \

-on_state {sw1_on vin {!swctrl}}

create_power_switch uart2_sw \

-domain {uart_2} \

-input_supply_port {vin VDD} \

-output_supply_port {vout VDD_2} \

-control_port {swctrl sw_ctrl2} \

-on_state {sw2_on vin {!swctrl}}

注意点1:\之后不要跟空格,不然仿真中会报错

注意点2:sw_ctrl1和sw_ctrl2需要在rtl中进行wire定义并assign赋值,这里vin{!swctrl}所以值为0时候为打开电源开关。

4.电源状态描述

### define power state ###

add_port_state {VDD} -state {TOF_HV 1.0} -state {TOP_OFF off}

add_port_state {VSS} -state {GND 0.0}

add_port_state {uart1_sw/vout} -state {VDD_1_HV 1.0} -state {VDD_1_OFF off}

add_port_state {uart2_sw/vout} -state {VDD_2_HV 1.0} -state {VDD_2_OFF off}

### define port state table for system ###

create_pst {uart_pst} -supplies {VDD VDD_1 VDD_2 VSS}

add_pst_state {add_on1} -pst {uart_pst} -state {TOP_HV VDD_1_HV VDD_2_HV GND}

add_pst_state {add_on2} -pst {uart_pst} -state {TOP_HV VDD_1_HV VDD_2_OFF GND}

add_pst_state {add_on3} -pst {uart_pst} -state {TOP_HV VDD_1_OFF VDD_2_HV GND}

add_pst_state {add_on4} -pst {uart_pst} -state {TOP_OFF VDD_1_HV VDD_2_HV GND}

注意点:add_port_state{uart1_sw/vout}这句话代表的就是VDD_1的值,但是不能直接用VDD_1,因为,VDD_1是一根线,not port,所以直接用会报错。

5.隔离单元

### define isolation constranints ###

set_isolation {uart1_iso_out} \

-domain {uart_1} \

-clam_value 0 \

-applies_to outputs \

-isolation_power_net {VDD} \

-isolation_ground_net {VSS}

set_isolation {uart1_iso_out} \

-domain uart_1 \

-isolation_signal {uart_iso_on_1} \

-isolation_sense low \

-location self

set_isolation {uart2_iso_out} \

-domain {uart_2} \

-clam_value 0 \

-applies_to outputs \

-isolation_power_net {VDD} \

-isolation_ground_net {VSS}

set_isolation {uart2_iso_out} \

-domain uart_2 \

-isolation_signal {uart_iso_on_2} \

-isolation_sense low \

-location self

注意点:uart_iso_on_1和uart_iso_on_2需要在rtl中定义wire类型并赋值,低电平表示隔离有效。

三.仿真

仿真参考之前写的文章:upf+vcs仿真

四.拓展阅读

推荐一:低功耗设计——基于UPF进行设计

推荐二:UPF基本概念学习

五.VCLP调试

问题(1)

add_pst_state {add_on4} -pst {uart_pst} -state {TOP_OFF VDD_1_HV VDD_2_HV GND}

这个状态虽然在vcs联合仿真中没有报错,但是VCLP中会显示worring,去掉。

问题(2)

-location self 应该改为-location parent。

顶层用self,其他用parent。