一、题目要求:

给出信号示意图以及波形示意图,用verilog实现两个串联的异步复位的T触发器的逻辑。

二、完成题目前的知识储备

1、书写规范

根据verilog代码书写规范,低电平复位信号用 rst_n ,高电平复位用rst。(这里题目低电平复位,但是仍用的rst,要注意),另外根据波形即可判断是低电平复位还是高电平复位。

2、关于异步复位和同步复位

always@(posedge clk)

begin

if(!rst_n)begin

...

end

else

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)begin

...

end

else

end

3、T 触发器

T触发器的主要功能是输出翻转控制。

数字电路中,在时钟有效边沿到来时,输入有效信号T取值的不同,那么电路就会具有不同的保持和翻转功能。

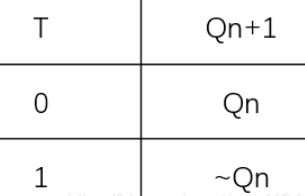

下图为T触发器的特性表,可看到T为输入有效信号,Qn为当前输出,Qn+1为下一时刻输出。当输入有效信号T=0时,能保持状态不变,当输入有效信号T=1时,可实现翻转功能。

T触发器的真值表:

| T |

Qn |

Qn+1 |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

根据真值表我们能够得到两个信息:

4、题目分析

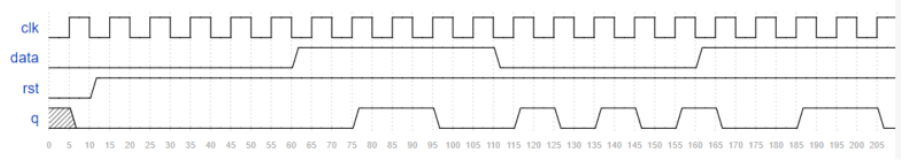

题目种给出了如下的信号示意图以及波形示意图

在信号示意图种加入中间存储变量q1

通过如下波形可看出,data相当于我们分析的T触发器中的输入有效信号T,rst信号为低电平复位信号。

因此本题的异步低电平复位的串联T触发器。

Verilog代码编写如下:

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst, //低电平复位最好用rst_n

output reg q

);

//*************code***********//

reg q1; //中间存储变量定义为reg型

//第一个T触发器

always @ (posedge clk or negedge rst)begin

if(!rst)

q1 <= 1'b0;

else if(data) //相当于T触发器中的输入有效信号为1的时候翻转,否则保持

q1 <= ~q1;

else

q1 <= q1;

end

//第二个T触发器

always @ (posedge clk or negedge rst)begin

if(!rst)

q <= 1'b0;

else if(q1) //相当于第一个T触发器的输出作为下一个T触发器输入

q <= ~q; //同时输入有效信号为1的时候,翻转,否则保持

else

q <= q;

end

//*************code***********//

endmodule