一、IP核的方式

1、打开IP核

含义:FIFO是一个先进先出的存储队列。与其他RAM不同的是FIFO没有地址,先入先出。

作用:作用就是作为数据的队列通道,让数据暂时缓存,以等待读取。用于异步FIFO模块来实现接口,接口双方都在自己的时钟下工作,他们之间不需要互相握手,只需要跟接口FIFO模块进行交互即可向FIFO模块中写入数据或从FIFO模块中读出数据。

命名规范:尽量写出写、读宽度以及深度,一目了然

接口:Native(不用总线类型)、AXIMemory Mapped and AXI Stream(总线类型)

一般使用Native。AXI interface FIFOs是由本地FIFO衍生而来的,AXI是xillinx特有的高速接口

区别AXI除了在Native支持的应用下使用,也可以在总线系统和点对点高速应用中使用

AXI接口FIFO不支持内置FIFO和移位寄存器FIFO配置。

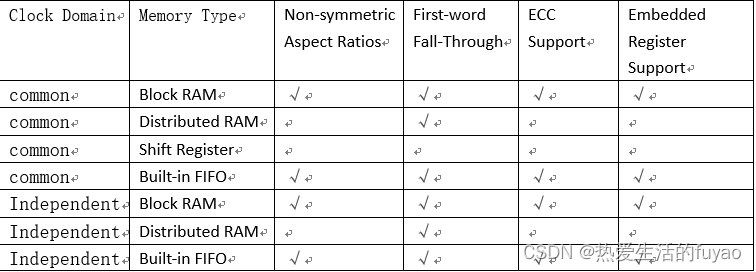

FIFO配置:

注意:Embedded Register Support 仅仅在Ultrascale family中使用

Xilinx仅支持UltraScale设备的Non-symmetric Aspect Ratios。(内置fifo的最大深度限制为8192)

FIFO有同步和异步两种方式。当读写时钟一致,或者数据没有跨时钟的时候就选择同步时钟即可,否则选择异步时钟。

Block RAM:使用FPGA内部的RAM

Distributed RAM:分布式RAM,使用内部的LUT和逻辑电路组成的fifo,当深度不大于128时可以使用

shift Register:移位寄存器形式,深度不大于32时可以使用

Built-in:内部自带的fifo,深度大于128可以使用

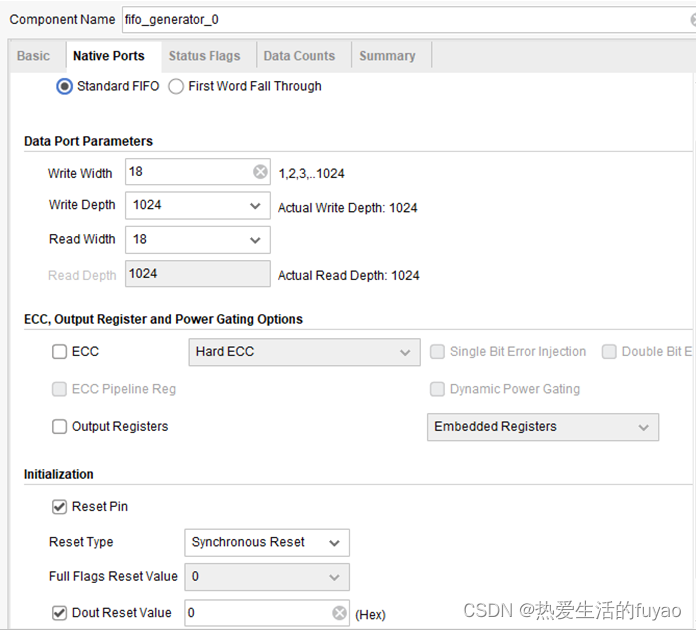

Read Mode 读模式

Standard FIFO :标准FIFO

First Word Fall Through :第一个写入数据将被从ram中提前读出到读数据线,第一个数据有效与empty无效同时,即当empty无效时, 不必读取,数据线上的数据已经有效,读信号有效后,读数据线将显示下一数据地址

Data Port Parameters 数据接口参数

write width 写宽度

write depth 写深度

read width 读宽度

read depth 读深度

(后面读的设置通常与写的设置相同)

Initialization 初始化

Reset Pin 复位引脚

Enable safety Circuit 启用安全电路 一般都要选上

Reset Type 复位类型,有两种

异步复位和同步复位

Full Flag Reset Value 复位的值,0为低电平复位,1为高电平复位

ECC,Output Register and Power Gating Options:输出寄存器和电源控制选项。

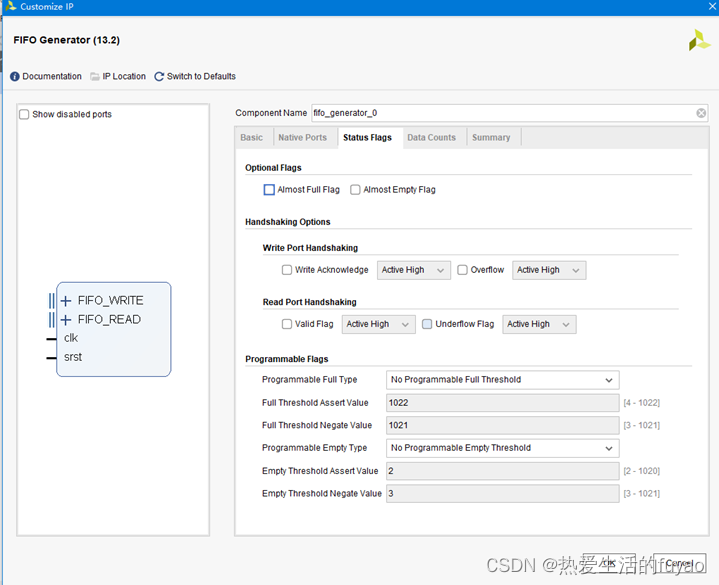

在status flags界面中主要是设置一些标志位,设置将满和将空,一般可用可不用,因为用空满信号就可以;红框2表示读出数据有效信号,这个标志位与读出数据同步,有数据读出就有效,否则无效,可用来判断从FIFO中是否有数据读出;红框3表示可编程满和可编程空,即空满的值可由用户设定,比如这里设置了可编程满的值为56,且是常数(还有一种是在代码模块中通过引脚输入),意思是FIFO中有55个数时,就表示满了而不是到64个才满,这能更好的避免数据溢出,可编程空原理一样,这里没有设置。

Data counts一般不用设置,用来累计读写数据的个数的,与空满信号功能重复,不用也可以。点击OK就可以生成IP了

打开工程Sources中的IP,双击.veo文件,找到IP例化程序端口,便于调用。

2、例化程序:

fifo_generator_0 fifo_generator_0_inst

(

.rst (1'b0),

//wr

.wr_clk (video_tx_clk),

.din (tpg_video_data),

.wr_en (hdmi_ce),

.full (full),

//rd

.rd_clk (hdmi_refclk),

.rd_en (1'b1),

.dout (tpg_video_data_out),

.empty (empty)

);

3、端口定义:

almost_full : 这个信号表明在FIFO满之前只能再执行一次写操作

almost_empty :当FIFO仅剩一个数据的时候就会拉高

prog_empty: 当FIFO中的数据个数小于参数PROG_FULL_THRESH时会拉高

prog_full : 当FIFO中的数据个数大于参数PROG_FULL_THRESH时会拉高

wr_cak : 写操作回应,表示上次写操作成功

**overflow ** :上溢,仅当fifo满的时候给wr_en时会拉高,此数据并不会被写入fifo

underflow : 下溢,仅当fifo空的时候rd_en时会拉高,此时并没有数据被读出来。

二、原语的方式

1、参考案例

---------------------------------------------------------------------//

async fifo distributed , deepth 32 , write width "DATA_WIDTH+1" bit ,read width "DATA_WIDTH+1" bit

---------------------------------------------------------------------//备注方式和深度和写读的宽度

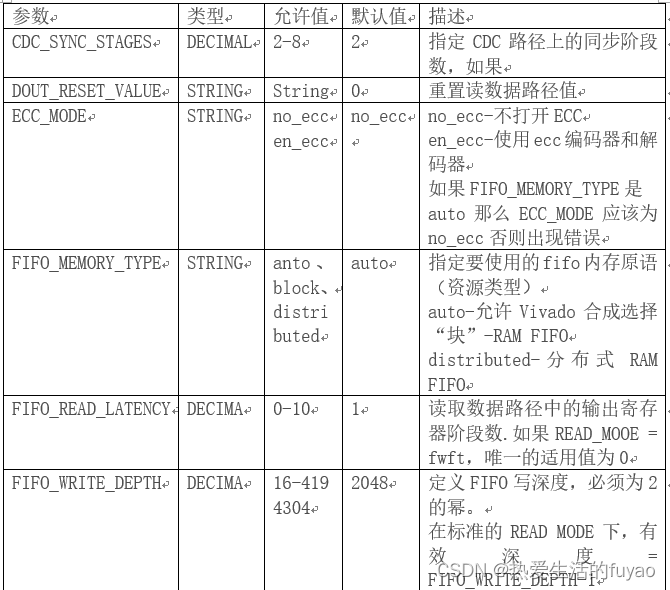

xpm_fifo_async #(

.CDC_SYNC_STAGES (2 ), // DECIMAL

.DOUT_RESET_VALUE ("0" ), // String

.ECC_MODE ("no_ecc" ), // String

.FIFO_MEMORY_TYPE ("distributed" ), // String auto block distributed

.FIFO_READ_LATENCY (1 ), // DECIMA

.FIFO_WRITE_DEPTH (ASYNC_FIFO_DEPTH ), // DECIMAL

.FULL_RESET_VALUE (1 ), // DECIMAL

.PROG_EMPTY_THRESH (ASYNC_FIFO_DEPTH/32 ), // DECIMAL

.PROG_FULL_THRESH (ASYNC_FIFO_DEPTH/32*31 ), // DECIMAL

.RD_DATA_COUNT_WIDTH (log2(ASYNC_FIFO_DEPTH)+1), // DECIMAL

.READ_DATA_WIDTH (DATA_WIDTH+1 ), // DECIMAL

.READ_MODE ("std" ), // String

.RELATED_CLOCKS (0 ), // DECIMAL

.SIM_ASSERT_CHK (1 ), // DECIMAL;

0=disable simulation messages, 1=enable simulation messages

.USE_ADV_FEATURES ("1000" ), // String

.WAKEUP_TIME (0 ), // DECIMAL

.WRITE_DATA_WIDTH (DATA_WIDTH+1 ), // DECIMAL

.WR_DATA_COUNT_WIDTH (log2(ASYNC_FIFO_DEPTH)+1) // DECIMAL

)

fifo_sd_20to10bit_tx0_inst (

.wr_clk (vdo_in_clk ),

.rst (reset_vinclk ),

.wr_en (fifo_wren ),

.din (fifo_wrdata ),

.full (fifo_full ),

.almost_full ( ),

.prog_full ( ),

.wr_ack ( ),

.wr_data_count ( ),

.wr_rst_busy ( ),

.overflow ( ),

//--------------------------------------------//

.rd_clk (gt_txclk ),

.rd_en (fifo_rden ),

.dout (fifo_rddata ),

.data_valid (fifo_dvalid ),

.empty (fifo_empty ),

.almost_empty ( ),

.prog_empty ( ),

.rd_data_count (fifo_rddata_cnt ),

.rd_rst_busy ( ),

.underflow ( ),

//--------------------------------------------//

.sleep ( ),

.injectdbiterr ( ),

.injectsbiterr ( ),

//--------------------------------------------//

.sbiterr ( ),

.dbiterr ( )

);

2、参数介绍

3、技巧方法

1、先把各个端口介绍,含义搞清楚

2、然后对应项目,把端口的具体值对应到项目中

3、按照格式,书写FIFO

4、编译生成bit文件再烧录到板子上即可

三、参考链接

fifo介绍及fifo IP核使用(工程文件获取请参考文末)

FIFO用法详解(附有代码)

XPM_ASYNC_FIFO学习笔记02