FPGA计数器边界问题解析

一次作者在处理AMBE2000数据接收过程中,遇到一个问题,对该计数器边界总是模糊不清。现在予以说明,以警示以后工作时书写错误代码。

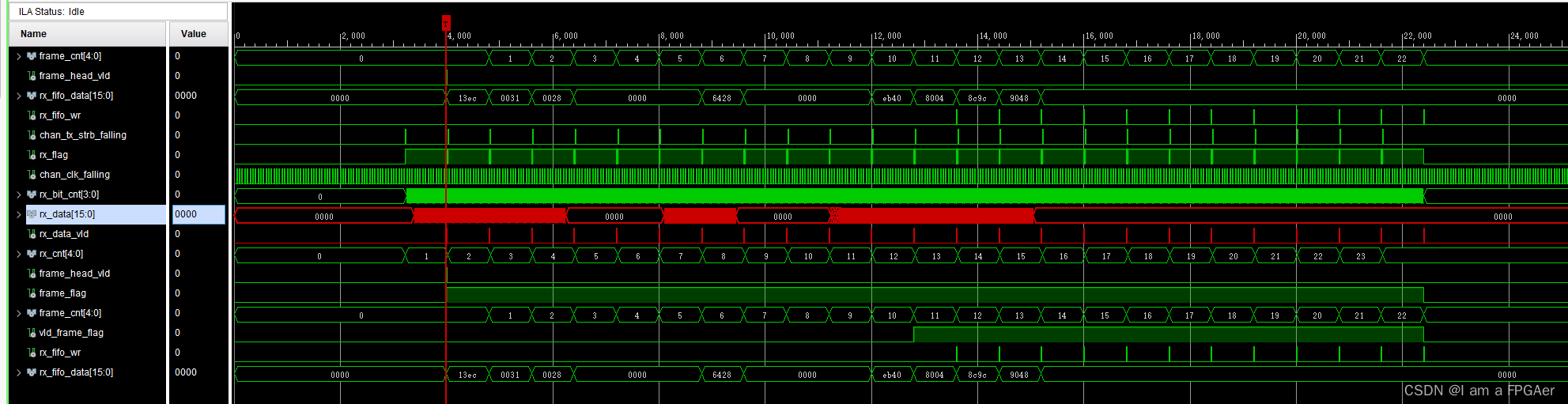

AMBE2000数据一旦准备好后,一次会输出24个字,其中第1个字0x13ec是同步头,连上同步头的前12个字为控制字,后12个字为数据字,我们需要提前数据字,抛弃控制字。作者的解决思路是:当捕获到0x13ec同步头后拉高一个flag,然后计数23次,完成整个接收过程。这其中需要拉个另一个flag,将后12个数据字表示出来。

问题:除去帧头标志外,还需要去掉11个字。计数器边界到底是卡在10还是11?模棱两可的。

always @(posedge clk or posedge rst) begin

if (rst==1'b1) begin

vld_frame_flag<=1'b0;

end

else if ( frame_flag==1'b1 && frame_cnt>='d11 ) begin

vld_frame_flag<=1'b1;

end

else begin

vld_frame_flag<=1'b0;

end

end

分析:需要去掉11字,那么计数器的边界肯定是11。以上代码验证是拉高时刻是正确的,frame_cnt是在data_vld条件下增加的,所以去掉前11个字,那么cnt11后立即拉高是可以的。也可以如下文所述:上一个时刻frame_cnt10,data_vld又再一次有效,也表示第11个数。

always @(posedge clk or posedge rst) begin

if (rst==1'b1) begin

vld_frame_flag<=1'b0;

end

else if ( frame_flag==1'b1 && data_lvd==1'b1 && frame_cnt>='d10 ) begin

vld_frame_flag<=1'b1;

end

else begin

vld_frame_flag<=1'b0;

end

end

结论:为统一期间,计数器的边界判断都需要带上计数条件,要判断n个数,判断条件就是: 条件 && n-1。