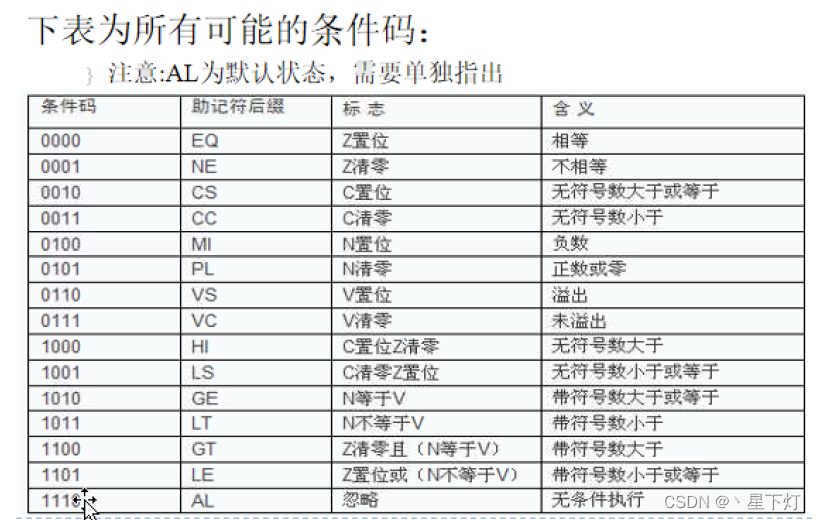

指令条件码

条件码就是一种简单的测试ALU状态标志位的方法。

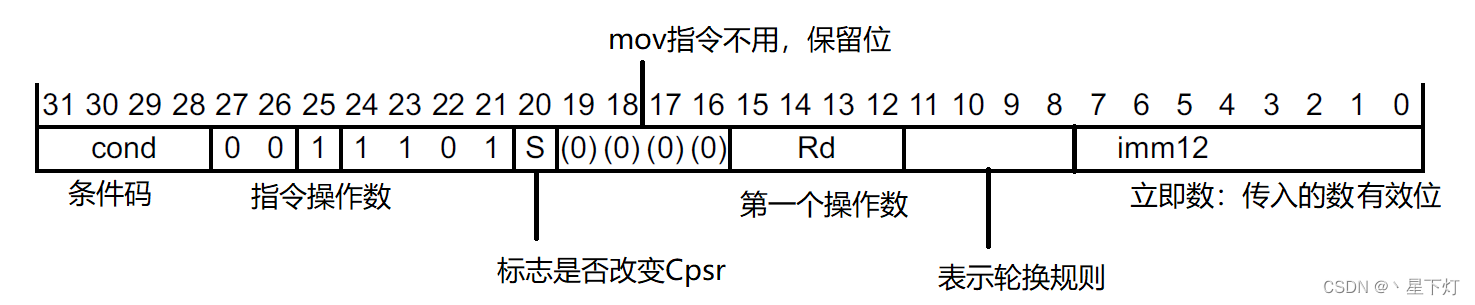

mov指令机器码

比如:

mov r1,#3

立即数:3

第一个操作数:寄存器1

S:0 (注意:mov指令后面加主机符为s时S位为1)

指令操作数:0011101,这是mov指令特有的

条件码:1110,无条件执行

所以它的指令机器码就是:1110 0011 1010 0000 0001 0000 0000 0011

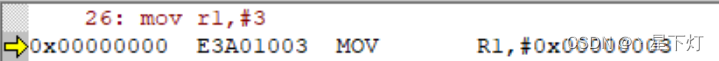

看一下keil编译的结果:(这里是16进制)E3A01003

有效立即数

立即数:在汇编指令中操作数是一个小于等于32bit的数,该数即为立即数。

合法立即数:该32位的立即数中最多只有8bit位的有效位,其他位是0的立即数。

@---mov 合法立即数---

mov r0,#0xFF

@mov r1,#0x1FF @ 有效位9位所以报错

mov r2,#0x003AC0000 @ 32位中有效位最多8位

mov r3,#0xF000000F @ 该数有连续24位0所以有效

@mov r4,#0xF00F0000 @ 这个没有连续24个0所以报错

mov r5,#0xFFFFFFFF @ 这是一个特殊的合法立即数

mov r5,#0xFFFFFFFD @ 也是合法的

mov r5,#0xFFFFFF00 @ 特殊值:最多连续8位0,而且其他位必须都不是0,而且这8个0必须连续

mov r6,#0xFFFF00FF @ 连续8位0所以合法

@mov r7,#0xFFF0F0FF @ 这就不合法

总结: 要不有有效位连续8位,要不连续24位0,要不是特殊值,满足其一即为有效立即数。

为什么mov指令只能将合法立即数装载到通用寄存器?

上面机器码对应关系可以看到,只有12bit位存放立即数,

而且这12bit被分为了两部分,存放立即数的位数只有0-7bit,8-11bit存放轮换规则,

如果这个立即数不合法,将会造成机器码错位。

所以mov指令存放的数必须是合法的。

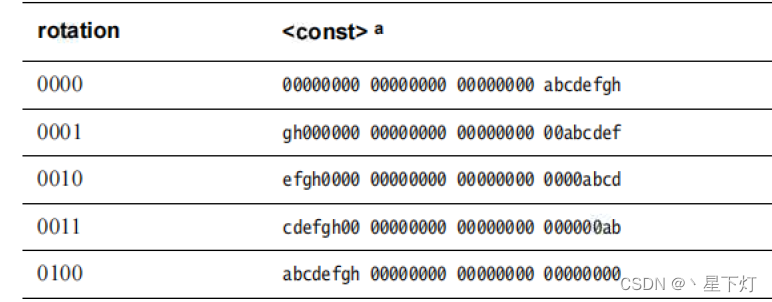

轮换规则

轮换规则:决定了立即数的样式

a-h表示8个有效位。

此时12bit的立即数就是 4位轮换规则+8位的有效位。

最后会根据轮换规则还原出的具体数。

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)